Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:36.

- Última modificação 2025-01-23 15:03.

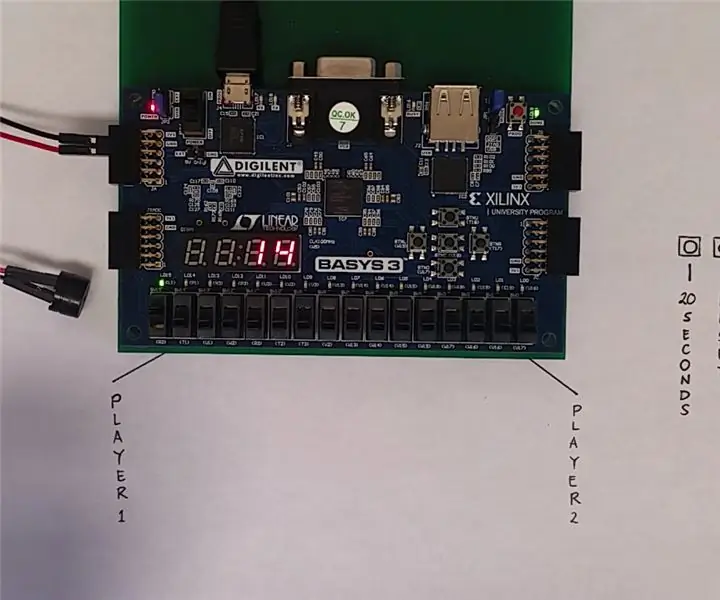

O sistema de campainha competitivo projetado neste projeto opera de maneira semelhante aos sistemas de campainha usados nas Competições Regionais e Nacionais do Science Bowl. Este projeto foi inspirado por meu envolvimento com a equipe de ciência do colégio por três anos. Sempre tivemos o desejo de recriar o sistema de campainha de bloqueio com um temporizador de 5 e 20 segundos.

Para dar algumas informações sobre o sistema de campainha, as campainhas do Science Bowl são programadas para inserir no máximo 8 jogadores (com 8 campainhas separadas). Assim que uma campainha for pressionada, a campainha da primeira pessoa acenderá para indicar qual jogador receberá a pergunta. O resto dos jogadores será "bloqueado", o que significa que seus buzzers não responderão até que o moderador reinicie o sistema de buzzer.

Depois que o moderador ler as perguntas, ele pressionará um botão para iniciar a contagem regressiva que será exibida no display de sete segmentos. Após uma pergunta "lançada", o moderador pode pressionar o botão direito para iniciar a contagem regressiva de 5 segundos. Enquanto isso, após uma pergunta "bônus", o moderador pode pressionar o botão esquerdo para iniciar a contagem regressiva de 20 segundos. Assim que o cronômetro chegar a zero, um sinal sonoro indicará que o tempo do jogador acabou.

Para reiniciar o sistema e a contagem regressiva, o moderador pode pressionar o botão central. Para reiniciar o mecanismo de bloqueio e os LEDs do jogador, os interruptores do jogador 1 e do jogador 2 devem estar na posição baixa.

Etapa 1: Materiais

Você precisará do seguinte:

- Placa Basys3 (ou placa FPGA equivalente)

- Cabo micro-B USB

- Alto-falante (usei um alto-falante passivo)

- 2 fios

- Software para implementar no FPGA (usei Vivado)

- Arquivo do Competitive Buzzer System

Etapa 2: Diagrama de caixa preta

O diagrama da caixa preta mostra as entradas e saídas que serão usadas neste sistema de campainha.

ENTRADAS:

player1, player2 Essas entradas são conectadas a dois interruptores na placa Basys3. Por conveniência, os interruptores mais à esquerda e mais à direita serão usados.

redefinir O botão central será usado para representar o botão de redefinir.

count_down_20_sec O botão esquerdo será usado para representar o botão do cronômetro de 20 segundos.

count_down_5_sec O botão direito será usado para representar o botão do cronômetro de 20 segundos. Para garantir que o cronômetro de 20 e 5 segundos inicie, segure o botão até que o display de sete segmentos mostre o cronômetro.

CLK A placa FPGA irá gerar um clock que funciona com uma freqüência de 10 ns.

SAÍDAS:

alto-falante A saída do alto-falante está conectada a uma campainha externa ou alto-falante. Você terá que conectar o alto-falante às portas pmod JA da placa Basys3. Esta etapa será descrita a seguir.

speaker_LED Esta saída é conectada a um LED no centro da placa e apenas indicará quando a saída do alto-falante do FPGA estiver alta. Você pode usar isso para testar seu alto-falante externo. Observe que algumas das portas pmod podem não funcionar bem, então você pode experimentar diferentes e usar o LED para verificar se o alto-falante deve estar ligado.

SEGMENTOS Esta saída é conectada aos oito segmentos individuais no display de sete segmentos, incluindo o ponto decimal.

DISP_EN Esta saída é conectada aos quatro ânodos no display de sete segmentos.

player_LED Esta saída é um sinal de 2 feixes que é conectado aos LEDs acima dos interruptores player1 e player2. O primeiro jogador a girar sua chave correspondente será indicado pelo LED. Observe que os dois LEDs não podem acender simultaneamente.

Etapa 3: Conectando o alto-falante externo

Para conectar o alto-falante externo à placa Basys3, pegue seus dois fios e conecte-os conforme indicado na imagem acima. A linha branca conecta o terminal negativo do alto-falante à porta de aterramento na placa. A linha vermelha conecta o terminal positivo do alto-falante à porta pmod JA10 na placa.

O arquivo de restrições é projetado para que qualquer porta de JA1 a JA10 funcione. No entanto, alguns pinos na placa não respondem, então se JA10 não funcionar, você pode tentar as outras portas.

Etapa 4: Diagrama Estrutural

A imagem acima mostra o diagrama estrutural do sistema de buzzer competitivo incluindo todos os componentes que compõem o módulo principal. Suas descrições são as seguintes:

player_lockout_LED1 O componente LED de bloqueio do player é uma máquina de estado finito que usa codificação one-hot. Ele tem quatro entradas: player1, player2, reset e CLK. Ele contém um player_LED de saída de pacote de 2 bits. As entradas e saídas do componente player_lockout_LED1 são todas diretamente conectadas às entradas e saídas com nomes idênticos do módulo principal.

buzzer_tone1 O componente buzzer é baseado neste código postado em um fórum

stackoverflow.com/questions/22767256/vhdl-… No entanto, foi modificado para emitir um som contínuo com uma frequência de 440 Hz (uma nota). A entrada de habilitação é conectada a um sinal buzzer_enable que é uma saída do componente down_counter_FSM1.

clk_div1 O componente divisor de relógio é uma versão modificada do divisor de relógio do Professor Bryan Mealy fornecido no PolyLearn. Ele desacelera o relógio para que o período de saída seja de 1 segundo.

down_counter_FSM1 O contador decrescente é um FSM projetado para contagem regressiva até zero. Os dois tempos de início possíveis são 20 ou 5, que são escolhidos pela entrada do usuário. Emite '1' quando o cronômetro chega a zero para indicar que o tempo acabou. Esta saída atua como uma habilitação para o componente de tom da campainha. O contador também produz um sinal de pacote de 8 bits que envia um BCD de 8 bits que é enviado ao decodificador de segmento. Outra saída é counter_on que também está conectada à entrada válida no decodificador de segmento.

sseg_dec1 O componente decodificador de sete segmentos é fornecido no PolyLearn e foi escrito pelo Professor Bryan Mealy. Ele usa uma entrada BCD fornecida pelo down_counter_FSM1 e produz o equivalente decimal no display de sete segmentos. Quando o contador está ligado, a entrada válida é alta. Isso permite que o decodificador exiba o número decimal no display de sete segmentos. Quando o contador está desligado, a entrada válida é baixa. O display de sete segmentos mostrará apenas quatro travessões.

Etapa 5: Diagrama de máquina de estados finitos (FSM)

A lista de sensibilidade para a máquina de estado finito inclui player1, player2, reset e o relógio. A saída FSM é um pacote player_LED de 2 bits conectado a dois LEDs na placa Basys3. A máquina de estados finitos mostra os três estados a seguir:

ST0 é o estado inicial. Nesse estado, os dois LEDs estão desligados. O FSM permanecerá neste estado se o jogador1 e o jogador2 estiverem baixos. Uma reconfiguração assíncrona também define o estado para ST0. Quando a chave player1 é definida como alta, o próximo estado será ST1. Se a chave player2 estiver definida como alta, o próximo estado será ST2.

ST1 é o estado para o qual o LED player1 está aceso. O FSM permanecerá neste estado para qualquer entrada. Isso significa que mesmo quando a chave player2 está definida para alto imediatamente após a chave player1 estar alta, ele permanecerá em ST1. Apenas a reconfiguração assíncrona pode definir o próximo estado para ST0.

ST2 é o estado para o qual o LED player2 está aceso. Semelhante ao ST !, O FSM permanecerá neste estado para qualquer entrada, mesmo quando a chave player1 for definida para alto imediatamente após a chave player2 estar alta. Novamente, apenas a reinicialização assíncrona pode definir o próximo estado para ST0.

Recomendado:

Nest Hello - Campainha da campainha com transformador integrado Reino Unido (220-240 V CA - 16 V CA): 7 etapas (com imagens)

Nest Hello - Campainha da campainha com transformador integrado Reino Unido (220-240 V CA - 16 V CA): eu queria instalar uma campainha Nest Hello em casa, um aparelho que funciona com 16 V a 24 V CA (NOTA: uma atualização de software em 2019 mudou a Europa faixa de versão para 12V-24V AC). A campainha padrão toca com transformadores integrados disponíveis no Reino Unido no

Sistema de alerta da campainha do corredor: 4 etapas

Sistema de aviso de campainha no corredor: Na escola, há campainhas que indicam quando a mudança de classe deve acontecer. Eles tocam primeiro para indicar quando a aula deve terminar e, em seguida, tocam uma segunda vez para indicar quando a próxima aula deve começar. Se um aluno está atrasado, então ele geralmente tem t

Transforme sua campainha com fio em uma campainha inteligente com IFTTT: 8 etapas

Transforme sua campainha com fio em uma campainha inteligente com IFTTT: A campainha WiFi transforma sua campainha com fio existente em uma campainha inteligente. https://www.fireflyelectronix.com/product/wifidoor

Transforme sua campainha com fio em uma campainha inteligente com o Home Assistant: 6 etapas

Transforme sua campainha com fio em uma campainha inteligente com o Home Assistant: Transforme sua campainha com fio existente em uma campainha inteligente. Receba uma notificação em seu telefone ou emparelhe-se com sua câmera existente na porta da frente para receber um alerta de foto ou vídeo sempre que alguém tocar sua campainha. Saiba mais em: fireflyelectronix.com/pro

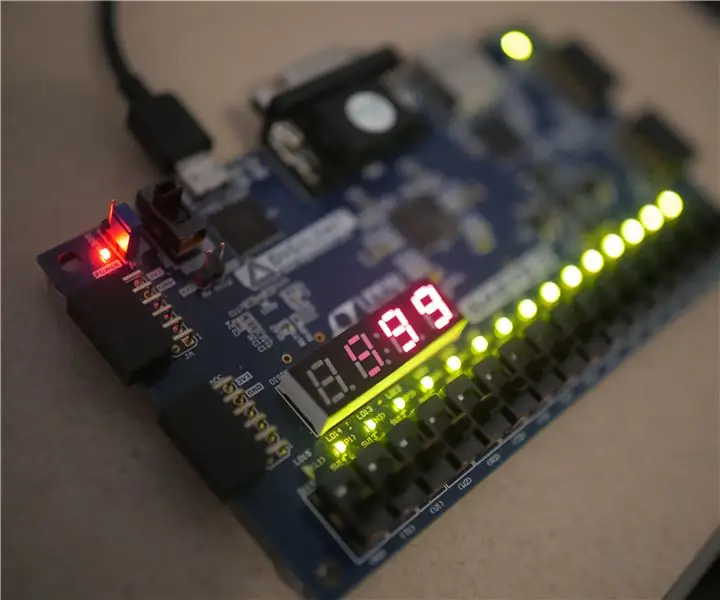

Jogo de cronometragem VS competitivo de 2 jogadores: 4 etapas

2 Player Competitive VS Timing Game: Você vai precisar de: 1.Digilent Basys 3, FPGA Board (ou qualquer outro FPGA) 2. Uma versão relativamente atualizada do Vivado ou algum outro ambiente VHDL3. Um computador que pode executar o programa mencionado