Índice:

- Etapa 1: Diagrama de blocos

- Etapa 2: Princípio de Operação

- Etapa 3: Implementação da lógica

- Etapa 4: Resolvendo o impasse

- Etapa 5: Configuração do dispositivo - Circuito Matrix0

- Etapa 6: Configuração do dispositivo - Lógica de clock do SPI

- Etapa 7: Configuração do dispositivo - Propriedades dos componentes Matrix0

- Etapa 8: Configuração do dispositivo - Circuito Matrix1

- Etapa 9: Configuração do dispositivo - Contador binário de 3 bits

- Etapa 10: Configuração do dispositivo - Lógica de comparação de 3 bits

- Etapa 11: Configuração do dispositivo - Lógica de comparação digital e registro temporário

- Etapa 12: Configuração do dispositivo - Propriedades dos componentes Matrix1

- Etapa 13: Resultados

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:35.

- Última modificação 2025-01-23 15:03.

Os sistemas de controle e dispositivos relacionados lidam com várias fontes de energia, como linhas de polarização ou baterias, e devem rastrear a linha mais alta (ou mais baixa) entre um determinado conjunto.

Por exemplo, a comutação de carga em um sistema alimentado por "várias baterias" requer que o sistema monitore a tensão mínima ou máxima entre a matriz de bateria (máxima ou mínima como uma função do algoritmo de comutação particular) e roteie dinamicamente a carga para o fonte mais apropriada em tempo real. Como alternativa, o sistema pode precisar desconectar temporariamente a bateria de menor tensão para o carregamento adequado.

Outro exemplo é o moderno sistema de energia solar, onde cada painel solar é equipado com um mecanismo de rotação giratória e com um circuito de rastreamento solar (este último fornecendo a informação da posição do Sol para orientar o painel). Com as informações de tensão máxima, cada posição do painel solar pode ser ajustada com base no painel da corda que realmente fornece a tensão de saída mais alta, alcançando assim um nível superior de otimização de energia.

Existem várias marcas diferentes de ICs comerciais (principalmente microcontroladores) que podem, em princípio, implementar um seguidor de tensão máxima. No entanto, eles exigem programação e são menos econômicos do que uma solução de sinal misto. Suplementar um projeto Dialog GreenPAKTM pode afetar positivamente a acessibilidade, o tamanho e a modularidade do projeto. Este projeto explora o benefício de integrar circuitos analógicos e digitais em um único chip.

Neste Instructable, o front-end analógico e a lógica digital necessários para implementar um localizador de tensão máxima (ou eventualmente mínima) entre oito fontes distintas são implementados.

Para implementar o monitor de tensão máxima / mínima analógico de 8 canais, um SLG46620G é usado.

Abaixo, descrevemos as etapas necessárias para entender como a solução foi programada para criar o monitor de tensão máxima / mínima analógico de 8 canais. No entanto, se você deseja apenas obter o resultado da programação, baixe o software GreenPAK para visualizar o arquivo de design GreenPAK já concluído. Conecte o GreenPAK Development Kit ao seu computador e acesse o programa para criar o monitor analógico de tensão máxima / mínima de 8 canais.

Etapa 1: Diagrama de blocos

A Figura 1 mostra o diagrama global do sistema implementado.

Uma sequência de até 8 fontes de tensão variável é multiplexada e conectada a um módulo ADC GreenPAK conectado a um design interno personalizado capaz de selecionar a fonte com a tensão mais alta em relação às outras. A lógica interna emite essas informações para exibição ou processamento posterior.

O design é baseado no produto GreenPAK SLG46620G, porque ele incorpora todos os blocos de construção analógicos e digitais necessários para a aplicação. Nesta implementação, o array é varrido por meio de um multiplexador analógico ADG508 acionado diretamente pelo GreenPAK IC.

A informação de saída é um número digital de 3 bits correspondente ao número da fonte de tensão na tensão máxima. Uma maneira direta de obter essas informações é mostrar o número por meio de um display de 7 segmentos. Isso pode ser facilmente realizado através da interface da saída digital do SLG46620G a um driver de exibição de 7 segmentos, como a solução GreenPAK descrita na Referência ou a um 74LS47 IC comum.

O circuito apresentado busca a tensão máxima. Para converter o projeto em um localizador de tensão mínima, um circuito de pré-condicionamento simples deve ser adicionado entre o multiplexador analógico e a entrada analógica GreenPAK, subtraindo a saída do multiplexador de uma tensão de referência de 1 V.

Etapa 2: Princípio de Operação

O projeto visa selecionar a fonte com tensão máxima, portanto, uma varredura é realizada em todo o array enquanto armazena o valor last-max e o compara com o próximo valor na entrada (que pertence à próxima fonte de tensão na varredura).

A seguir, iremos nos referir a uma seqüência completa de multiplexação ao longo de todas as entradas como uma “varredura” ou “loop”.

A comparação entre dois valores não é realizada por meio dos componentes ACMP (porém, disponíveis no SLG46620G), mas sim pelo módulo DCMP, uma vez que os valores são digitalizados respectivamente. Esta é uma técnica avançada e refinada abordada pela primeira vez na Referência.

A Figura 2 mostra como o SLG46620G está estruturado para este projeto.

O sinal de entrada analógico vai para a entrada ADC através do componente PGA com um ganho definido de 1. Várias configurações de ganho também são possíveis para encontrar a melhor correspondência com os eletrônicos de condicionamento front-end dedicados a mapear as tensões de entrada para 0-1 V alcance do módulo GreenPAK ADC.

O ADC opera no modo de terminação única e converte o sinal analógico em um código digital de 8 bits, que é então transferido para o módulo DCMP. O código digital também é alimentado no bloco SPI, configurado como Buffer ADC / FSM, onde um código digital pode ser armazenado e não será alterado até que o próximo pulso chegue à entrada SPI CLK. Observe que um bloco lógico dedicado conduz a entrada SPI CLK. Iremos investigar esta parte mais tarde, pois esta é a lógica “central” responsável pela operação adequada. Um novo código digital é armazenado no módulo SPI apenas se pertencer à tensão de entrada máxima real.

O componente DCMP é usado para comparar os dados ADC atuais com o último vencedor (ou seja, o último máximo encontrado) que é armazenado no bloco SPI. Ele irá gerar um pulso na saída OUT + quando os novos dados do ADC forem maiores do que os anteriores. Usamos o sinal OUT + para atualizar o bloco SPI com o novo vencedor.

Um sinal de relógio global conduz as conversões ADC e tempos gerais. Uma vez que uma conversão é realizada, o sinal de saída INT do ADC pulsa, coordenado em tempo com a saída de dados paralela do ADC. Usamos a saída INT também para incrementar um contador binário de 3 bits, implementado por DFFs em Matrix1, que é útil por três razões:

1. As linhas de saída do contador endereçam o multiplexador analógico externo, servindo assim a próxima tensão de entrada para o ADC;

2. A contagem é congelada em um registro de 3 bits (implementado em Matrix1) para armazenar o vencedor temporário durante uma varredura;

3. A contagem é decodificada para atualizar um segundo registro de 3 bits (implementado no Matrix0) assim que a varredura for concluída.

Etapa 3: Implementação da lógica

O módulo ADC fornece sequencialmente os dados convertidos de todas as tensões de entrada, uma após a outra, indefinidamente. Uma vez que o Multiplexador é endereçado a 0b111 (decimal 7), o contador passa para 0b000 (decimal 0), iniciando assim uma nova varredura das tensões de entrada.

Durante a varredura, o sinal de saída ADC INT é gerado quando a saída de dados paralela é válida. Quando este sinal pulsa, o multiplexador analógico deve mudar para a próxima entrada, fornecendo ao PGA a tensão correspondente. Portanto, a saída ADC INT é o sinal de clock direto do Contador Binário de 3 bits da Figura 2, cuja palavra de saída paralela de 3 bits endereça diretamente o multiplexador analógico externo (“V select” na Figura 1).

Vamos agora nos referir a um exemplo em que as tensões de entrada devem ter as seguintes relações:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

A Figura 3 representa os principais sinais envolvidos no mecanismo de decisão máxima.

Uma vez que os dados são eventualmente sincronizados no registro do buffer SPI de forma síncrona com os pulsos INT, existe uma janela de comparação onde o conteúdo do buffer SPI é comparado com o próximo resultado de conversão ADC. Este tempo particular resulta na geração de pulsos OUT + na saída DCMP. Podemos tirar proveito desses pulsos para carregar novos valores no registro de buffer SPI.

Como aparente a partir da linha de dados do buffer SPI da figura anterior, o registro SPI sempre contém, vez a tempo, o maior valor entre as 8 entradas e é atualizado apenas quando um valor maior é detectado pelo módulo DCMP (referindo-se ao DCMP OUT + linha de saída do gráfico, os pulsos ausentes fazem com que V2 permaneça travado no registro até que seja comparado com V5).

Etapa 4: Resolvendo o impasse

Se a lógica implementada fosse como a descrita acima, é claro que entraríamos em uma situação de deadlock: o sistema é capaz de detectar apenas tensões maiores do que a correspondente ao que está armazenado no registrador do buffer SPI.

Isso também é válido caso essa tensão diminua e então outra entrada, até agora inferior, se torne a mais alta: ela nunca seria detectada. Essa situação é melhor explicada na Figura 4, onde apenas 3 tensões de entrada estão presentes para fins de clareza.

No momento da iteração 2, V3 cai e V1 é a tensão máxima real. Mas o módulo DCMP não fornece um pulso porque os dados armazenados no registro de buffer SPI (correspondente a 0,6 V) são maiores do que o correspondente a V1 (0,4 V).

O sistema então se comporta como um localizador de máximas “absoluto” e não atualiza a saída corretamente.

Uma boa maneira de superar esse problema é forçar o recarregamento dos dados no SPI Buffer Register quando o sistema completar um ciclo de polling completo de todos os canais.

Na verdade, se a tensão naquela entrada ainda for a mais alta, nada muda e o controle continua com segurança (referindo-se à Figura 4 acima, este é o caso das Iterações de Loop 0 e 1). Por outro lado, se a tensão nessa entrada por acaso diminuir para um valor menor do que outra entrada, então recarregar o valor dá a possibilidade ao módulo DCMP de produzir um pulso OUT + ao compará-lo com o novo valor máximo (este é o caso das Iterações de Loop 2 e 3).

Um pedaço de circuito lógico é necessário para superar o problema. Ele deve gerar um sinal de clock para o componente SPI quando o loop atingir a entrada máxima real, forçando assim um recarregamento de sua palavra de dados atualizada no registrador de buffer SPI. Isso será discutido nas Seções 7.2 e 7.6 abaixo.

Etapa 5: Configuração do dispositivo - Circuito Matrix0

O SLG46620G possui dois blocos Matrix, conforme ilustrado na Figura 2. As Figuras a seguir mostram as respectivas configurações do dispositivo.

A parte superior do circuito é o “Registro de Loop” realizado com 3 DFFs (DFF0, DFF1 e DFF2). Ele é atualizado após cada loop do multiplexador de entrada para enviar a um driver de exibição de 7 segmentos o número binário do “vencedor”, que é a entrada com maior tensão na última varredura. Tanto o clock para os DFFs quanto os dados vêm da lógica implementada no Matrix1 por meio, respectivamente, das portas P12, P13, P14 e P15.

A parte inferior é o front end analógico com entrada no pino 8 e PGA com ganho x1. A saída ADC INT vai para a lógica de clock do SPI e para Matrix1 através da porta P0, onde servirá como o sinal de clock para o contador implementado.

As saídas de dados paralelas ADC e SPI são respectivamente rotuladas como NET11 e NET15 para serem conectadas ao componente DCMP no Matrix1.

Etapa 6: Configuração do dispositivo - Lógica de clock do SPI

Conforme apontado anteriormente na seção “Implementação lógica”, o SPI Buffer Register é atualizado toda vez que uma comparação entre o valor real armazenado e os novos dados de conversão ADC gera um pulso na saída DCMP OUT +.

A integridade do sinal é garantida se este sinal for AND com a saída ADC INT. Isso evita qualquer pico e acionamento falso.

Também enfatizamos que, para pular as situações de deadlock, o buffer SPI deve ser atualizado quando o loop atingir os dados vencedores reais.

Então, três sinais estão em jogo para a temporização SPI adequada:

1. Saída ADC INT (LUT0-IN1)

2. Saída DCMP OUT + (LUT0-IN0 via porta P10)

3. A contagem é igual ao sinal de trava (LUT0-IN2 via porta P11)

Os dois primeiros são AND-ed e ambos OR-ed com o último em LUT0, cuja implementação é configurada como na Figura 6.

Etapa 7: Configuração do dispositivo - Propriedades dos componentes Matrix0

As Figuras 7-10 mostram as demais janelas de propriedades dos componentes pertencentes ao Matrix0.

Etapa 8: Configuração do dispositivo - Circuito Matrix1

Etapa 9: Configuração do dispositivo - Contador binário de 3 bits

A parte superior do circuito contém elementos lógicos, principalmente um contador binário de 3 bits sincronizado pela saída ADC INT, como já discutido. Este contador é implementado com um esquema bastante "padrão" mostrado na Figura 12.

Este contador é realizado em nosso projeto por meio de flip-flops DFF9, DFF10, DFF11 e INV1, LUT4, LUT8. A saída DFF9 é o LSB enquanto DFF11 é o MSB, conforme mostrado na Figura 13.

LUT4 é configurado como um XOR enquanto LUT8 executa a lógica AND-XOR da Figura 12.

As saídas do contador vão para três pinos de saída digital para endereçar o multiplexador analógico externo.

LUT10 decodifica o código do contador quando uma varredura é concluída e alimenta um pulso para Matrix0 via DLY8 e porta P12. Isso é feito simplesmente fazendo o AND das saídas do contador, decodificando assim o número 7 dec (0b111 binário, fim do loop).

Etapa 10: Configuração do dispositivo - Lógica de comparação de 3 bits

A Figura 15 mostra o circuito usado para detectar quando o loop está iterando no endereço “vencedor” atual. Nesse caso, como já discutido, um pulso digital deve forçar um recarregamento do resultado do ADC atual para resolver uma possível situação de deadlock.

O endereço “vencedor” é armazenado no registro temporário da Matriz1 (veja abaixo), enquanto o endereço atual é gerado pelo contador binário.

As portas XNOR fornecem uma saída verdadeira (lógica 1 ou 'alta') quando ambas as entradas são iguais. Fazer o AND desse sinal para todos os bits (LUT9) nos dá um pulso quando os dois códigos binários são iguais. Detalhes sobre portas XOR como verificadores de paridade podem ser encontrados na Referência.

O sinal ‘Counter-equals-Latch’ é passado para Matrix0 através da porta P11.

Etapa 11: Configuração do dispositivo - Lógica de comparação digital e registro temporário

A parte inferior da Figura 11 (destacada na Figura 16) mostra o bloco DCMP, a parte de tomada de decisão deste projeto.

DFF6, 7 e 8 formam um registro de 3 bits para armazenar o número de entrada temporário “vencedor” enquanto o loop está em execução. A entrada para os flip-flops são as saídas do contador binário de 3 bits, conforme visíveis no circuito Matrix1 global da Figura 11, aqui puladas para fins de clareza.

As saídas deste registro não podem conduzir diretamente o display de 7 segmentos porque o valor armazenado aqui muda durante uma varredura e deve ser considerado 'válido' apenas no final da própria varredura.

Por este motivo, as saídas do registro temporário se conectam ao Registrador de Loop do Matrix0 através das portas entre matrizes P13, P14 e P15.

É importante observar na Figura 16 que o registro temporário é sincronizado pela saída DCMP OUT + quando a comparação dos registros ADC-SPI resulta em um novo máximo encontrado.

O mesmo sinal OUT + é passado para Matrix0, SPI CLK Logic, via porta P10.

Etapa 12: Configuração do dispositivo - Propriedades dos componentes Matrix1

As Figuras 17-19 mostram as janelas de propriedades dos componentes pertencentes ao Matrix1.

Etapa 13: Resultados

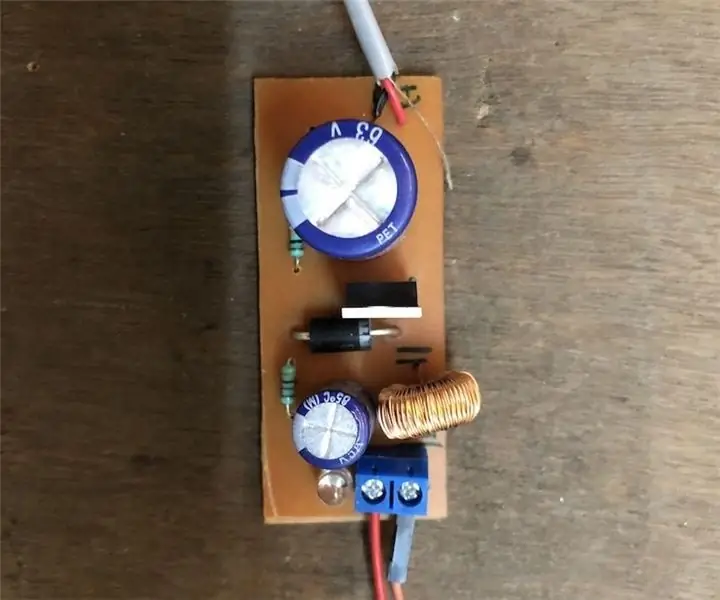

Para testar a implementação, um protótipo de placa de avaliação foi construído, onde as 8 tensões de entrada analógica são obtidas por uma série de divisores de resistor com TrimPots (conforme mostrado na Figura 20).

O multiplexador utilizado é um ADG508, peça que pode operar com alimentação única (12 V).

O driver de exibição de 7 segmentos é um 74LS47. Ele decodifica uma palavra de entrada paralela e direciona diretamente um display de 7 segmentos de ânodo comum.

A placa de avaliação tem um conector de ângulo reto 2x10 para conectar diretamente a uma plataforma de desenvolvimento avançada GreenPAK em seu conector de expansão, conforme mostrado na Figura 21.

A conjunção com a plataforma de desenvolvimento avançado GreenPAK torna muito simples fazer medições dos sinais para uma verificação rápida. Por exemplo, a Figura 22 mostra um conjunto de sinais (respectivamente CLOCK, saída ADC INT e saída DCMP OUT +) capturados por um HP 54620A Logic Analyzer. As formas de onda são acionadas por uma borda ascendente do sinal OUT + (no osciloscópio rotulado como ‘A> B’), portanto, esta é uma captura de forma de onda quando uma nova tensão máxima é detectada entre as entradas analógicas. Na verdade, ele foi obtido girando um dos TrimPots da Placa de Avaliação para aumentar a tensão correspondente mostrada na Figura 22.

A Figura 23 mostra o esquema da Placa de Avaliação.

Conclusão

Neste Instructable, implementamos um localizador de tensão máxima (ou mínima) de oito canais para ser usado como um acréscimo comum aos sistemas de controle multicanal. A abordagem apresentada explora recursos avançados dos componentes GreenPAK e mostra como é possível integrar em um único chip funções analógicas e digitais. Vários ICs comerciais podem ser substituídos por Dialog GreenPAKs para que o tamanho e o custo do aplicativo possam ser reduzidos.

Recomendado:

Monitor de tensão para baterias de alta tensão: 3 etapas (com fotos)

Monitor de tensão para baterias de alta tensão: Neste guia, explicarei como construí meu monitor de tensão de bateria para meu longboard elétrico. Monte como quiser e conecte apenas dois fios à bateria (Gnd e Vcc). Este guia presumiu que a voltagem da bateria excede 30 volts, w

DC - DC Tensão Reduzida Modo de Interruptor Conversor de Tensão Buck (LM2576 / LM2596): 4 etapas

DC - DC Voltage Down Switch Mode Conversor Buck Voltage (LM2576 / LM2596): Fazer um conversor Buck altamente eficiente é uma tarefa difícil e até mesmo engenheiros experientes requerem vários projetos para chegar ao certo. Um conversor Buck (conversor abaixador) é um conversor de energia DC para DC, que reduz a tensão (enquanto aumenta

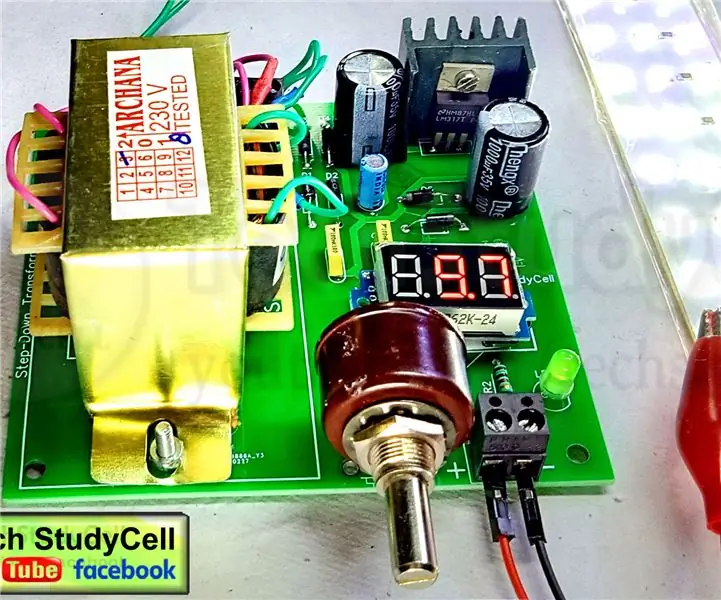

Fonte de alimentação DC de tensão ajustável usando o regulador de tensão LM317: 10 etapas

Fonte de alimentação DC de tensão ajustável usando o regulador de tensão LM317: Neste projeto, eu projetei uma fonte de alimentação DC de tensão ajustável simples usando o LM317 IC com um diagrama de circuito de fonte de alimentação LM317. Como este circuito possui uma ponte retificadora embutida, podemos conectar diretamente a alimentação 220V / 110V AC na entrada

LEIA TENSÃO ANALÓGICA - ARDUINO - REVELAÇÃO DO CÓDIGO # 1: 5 etapas

READ ANALOG VOLTAGE - ARDUINO - CODE REVEAL # 1: CODE REVEAL # 1 LEIA TENSÃO ANALÓGICA: Este exemplo mostra como ler uma entrada analógica no pino analógico 0, converter os valores de analogRead () em tensão e imprimi-los no serial monitor do software Arduino (IDE)

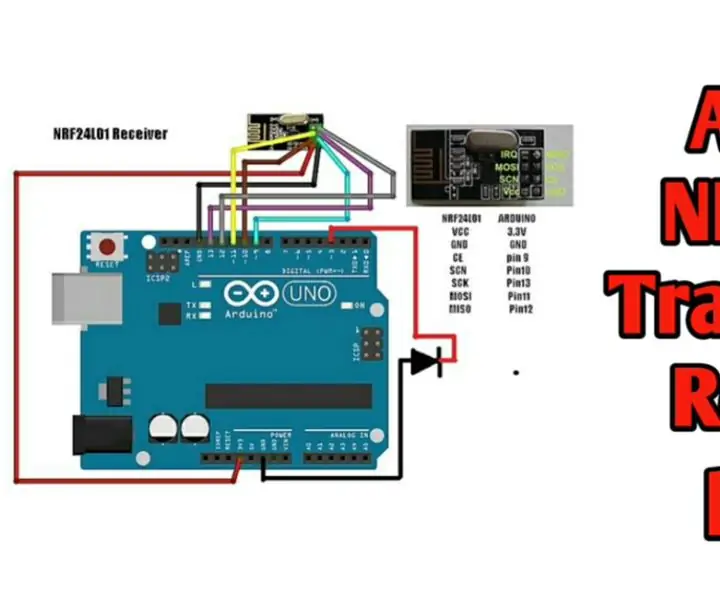

Remoto sem fio usando módulo 2.4 Ghz NRF24L01 com Arduino - Nrf24l01 Receptor transmissor de 4 canais / 6 canais para Quadcopter - Helicóptero Rc - Avião Rc usando Arduino: 5 etapa

Remoto sem fio usando módulo 2.4 Ghz NRF24L01 com Arduino | Nrf24l01 Receptor transmissor de 4 canais / 6 canais para Quadcopter | Helicóptero Rc | Avião Rc Usando Arduino: Para operar um carro Rc | Quadcopter | Drone | Avião RC | Barco RC, sempre precisamos de um receptor e transmissor, suponha que para RC QUADCOPTER precisamos de um transmissor e receptor de 6 canais e esse tipo de TX e RX é muito caro, então vamos fazer um em nosso