Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:36.

- Última modificação 2025-01-23 15:03.

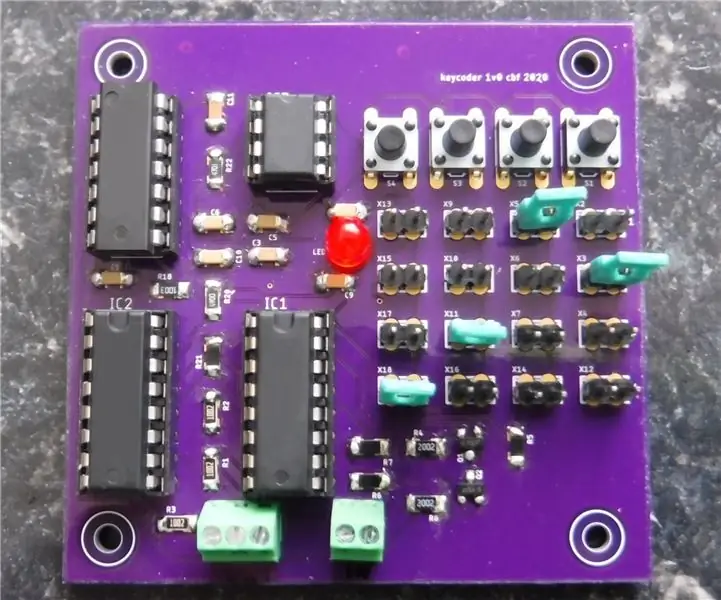

Este é um código simples de combinação de 4 botões programáveis.

módulo de interface e, como tal, pode ser usado em vários projetos onde um controle de bloqueio sem chave pode ser necessário. Apenas o PCB para gerar o sinal necessário para iniciar um mecanismo de travamento é mostrado, o mecanismo de travamento é deixado para o usuário.

O PCB usa uma combinação de montagem de superfície e componentes de orifício passante que estão disponíveis, uma mão firme e um ferro de solda de ponta fina serão necessários para montar os componentes SMT. Para facilidade de construção, os DIPs são montados em soquetes. Terminais de parafuso são usados para conectar a bateria de 9 V (5 V mín. A 15 V máx.) E a saída.

Criei o layout PCB usando Eagle Cad e foi fabricado no OSH Park.

Suprimentos

Lista de Componentes

3 × 10k Resistor 1206

2 × 20k Resistor 1206

4 × SWITCH SPST-NO

Bloco de terminais de PCB de 1 × 3 vias Passo de 2,54 mm

Bloco de terminais de PCB de 1 × 2 vias Passo de 2,54 mm

2 × 16 pinos IC Soquete opcional

1 × soquete IC de 14 pinos opcional

1 × 8 pinos IC Soquete opcional

1 × placa de camada 2 PCB

2 × 47k Resistor 1206

1 × 10n Capacitor 1206

1 × 100n Capacitor 1206

2 × BSS123 NFET SOT23

2 × CD4027 Dual JF Flip Flop 16DIP

1 × CD4081 Quad 2 entrada E 14DIP

1 × 555 Timer 8DIP

1 × LED VERMELHO 3mm

16x pinos do terminal com espaçamento de 2,54 mm

Etapa 1: Descrição do circuito

O circuito é realizado usando portas lógicas CMOS, um chip temporizador e um punhado de componentes discretos.

O elemento central é o flip-flop JK, dos quais quatro são usados. Isso requer o CD4027 que contém dois flip-flops, portanto, dois deles são necessários.

O CD4027 está disponível com 16 pinos em DIP e SMD, o pino e a funcionalidade são os mesmos, independentemente do pacote.

A tabela verdade mostra o estado da operação.

LH = transição de baixo para alto, HL = transição de alto para baixo, NC = sem alteração, X = não me importo.

Para esta aplicação, as entradas S e R são baixas, portanto, neste caso, as três últimas linhas da tabela verdade podem ser ignoradas.

Portanto, o estado de saída do Flip Flop (FF) será determinado pelo nível alto na entrada J ou K quando o relógio (CLK) estiver na borda de subida (LH).

Cada uma das três primeiras teclas do teclado são conectadas à entrada J de um FF que detecta o estado da tecla, com a tecla não pressionada a entrada é baixa (o padrão é puxado para baixo por um resistor), quando a tecla é pressionada A entrada J fica alta quando CLK muda para LH. Isso faz com que a saída Q fique alta.

O 2º FF é acionado por uma combinação do estado do 1º FF anterior e CLK por meio de uma porta AND.

O CD4081 quad 2 input AND está disponível com 14 pinos em DIP e SMD, o pin out e a funcionalidade são os mesmos, independentemente do pacote

Se a saída do 1 ° FF foi alta, a saída do 2 ° FF irá alta quando cronometrada, se a 2ª tecla foi pressionada.

O 3º FF é fechado por um 2º AND gate (através da saída do 2º FF) e CLK.

As entradas K de todos os FFs são conectadas juntas através da 4ª tecla, pressionando-a fornece um nível alto que no próximo LH da entrada CLK força as saídas Q baixas e redefine todos os FFs. Se a tecla não for pressionada, a entrada será mantida baixa (o padrão é puxado para baixo por um resistor).

Além do reset manual fornecido pela 4ª chave, um power on reset (POR), é fornecido pelo capacitor / resistor (CR), rede formada pelo capacitor na chave 4 e o resistor pull-down nas entradas K.

Quando a energia é aplicada, a rede CR fornece um pulso HL para as entradas K e com as entradas J todas puxadas para baixo por um resistor (J = L, K = H), as saídas Q são todas baixas.

A saída do 3º FF é conectada a uma entrada de um EXOR de 2 entradas, a outra entrada é conectada a uma rede POR.

EXORs de porta única estão disponíveis, mas sua tensão de operação máxima é de 5,5 V, que está na extremidade inferior da tensão de operação do CMOS. Em qualquer caso, a intenção é operar o circuito em 9V

Para este fim, um EXOR usando resistores, NFET's e a 3ª porta AND foi criado.

A saída das portas EXOR CLK através da 4ª porta AND para a entrada do 4º FF foram J = H e K = LH alterna a saída do FF. Quando Q = L o bloqueio é ativado, quando Q = H o bloqueio é desativado.

O relógio é gerado usando um temporizador 555 configurado no modo Astable.

Etapa 2: Montagem

Fixe os dispositivos de montagem em superfície primeiro, isso evita o bloqueio desses componentes pelos componentes maiores do orifício de passagem e, neste estágio, a placa é plana, o que simplifica a montagem.

Em seguida, solde os soquetes do IC, a menos que os encaixe diretamente na placa.

No entanto, os soquetes de IC podem simplificar a depuração e a substituição em caso de problemas.

Encaixe os pinos do terminal, a menos que use links de fios.

Os blocos de terminais são os últimos a serem soldados, pois ficam mais altos do que os outros componentes.

Etapa 3: Operação

A condição se a unidade está ativada ou desativada é indicada por um LED, que pode ser estendido acima ou remotamente da placa principal conforme os requisitos.

O LED permanece aceso quando definido. (também o padrão de inicialização).

A configuração e a desativação são realizadas inserindo uma combinação de 4 botões, o código correto liga o LED indicando que o sistema está configurado e o código correto desliga o LED.

Uma sequência de código incorreta aplica uma reinicialização ao sistema exigindo que a sequência de código seja inserida novamente desde o início.

O código necessário é definido por jumpers (permitindo que o código seja alterado facilmente) ou links (hard coded, menos flexível).

A codificação rígida nega os postes do terminal, simplificando a construção, mas torna a alteração do código menos conveniente

Os links são organizados em grupos de dois em uma matriz 4 x 4.

A coluna se alinha com o switch correspondente, uma coluna por switch.

A linha se alinha com a ordem de troca de 1 a 4.

Tomando S1 como exemplo.

Em S1, existem 4 links na coluna correspondente, se o primeiro link for feito, ele o atribui como o primeiro botão na sequência de código, Se o segundo link for feito, ele atribuirá S1 como o segundo botão na sequência, etc.

A mesma metodologia se aplica a todos os botões.

Etapa 4: solução de problemas

Podem ocorrer problemas e, se ocorrerem, como podem ser resolvidos.

A primeira coisa a fazer é procurar o óbvio.

IC no local errado, orientação errada ou pino (s) não soldado ou mal soldado, inserção de soquete incorreta ou pino torto.

Componente na posição errada, valor errado, orientação errada ou solda fraca.

Ponte de solda, Tensão de alimentação nos terminais errados, fios de alimentação trocados, tensão incorreta.

Até mesmo o PCB pode ter uma (s) faixa (s) aberta (s) ou em curto

Não diga a si mesmo que não pode ser um problema específico sem verificá-lo

Recomendado:

Fechadura de porta feita em casa por RFID: 4 etapas

RFID Home Made Door Lock: O dispositivo RFID Door Lock é um dispositivo prático que você pode usar na sua vida diária. Ao digitalizar seu cartão-chave, você pode abrir a fechadura da porta. Modifiquei o projeto deste site: https://atceiling.blogspot.com/2017/05/arduino-rfid.html?m=1Yo

Estação de Trabalho Eletrônica para Hobbyist - Estação De Trabalho Para Entusiastas Em Eletrônica: 10 etapas

Estação de Trabalho Eletrônica para Hobbyist - Estação De Trabalho Para Entusiastas Em Eletrônica: Atenciosamente Leitor e Hobbyist Eletrônica Nestas instruções apresento a construção de uma estação de trabalho para amadores eletrônicos, A estação contém as ferramentas e suportes comuns para trabalhar com circuitos eletrônicos: suporte giratório para ci impresso

Wifi para RF - Fechadura: 3 etapas (com fotos)

Wifi para RF - Bloqueio de porta: Visão geral Este instrutível dará a você a capacidade de bloquear / desbloquear sua porta da frente por meio de seu software de automação residencial (como OpenHAB - software de automação residencial gratuito que eu uso pessoalmente) A imagem acima mostra uma captura de tela de amostra do OpenHAB

Fechadura eletrônica RFID da porta: 9 etapas

Fechadura de porta eletrônica RFID: Hoje vou ensinar como eu projetei e construí a " MÁXIMA FECHA ELETRÔNICA DE PORTA " siga-me neste tutorial passo a passo, explicarei todos os detalhes e problemas que tive durante a construção. Espero que gostem! Como você pode ver no

Controle uma fechadura eletrônica Schlage com um Arduino !: 7 etapas

Controle uma fechadura eletrônica Schlage com um Arduino !: Este instrutível irá guiá-lo através do processo de desmontagem e hackeamento de uma fechadura eletrônica Schlage para controlá-la com um arduino