Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:37.

- Última modificação 2025-01-23 15:03.

Analisarei como o desafio do projeto da fonte de alimentação atende pela DC-DC Technologies.

Os projetistas de sistemas de energia enfrentam pressão constante do mercado para encontrar maneiras de aproveitar ao máximo a energia disponível. Em dispositivos portáteis, maior eficiência estende a vida útil da bateria e coloca mais funcionalidade em pacotes menores. Em servidores e estações base, os ganhos de eficiência podem economizar diretamente em infraestrutura (sistemas de refrigeração) e custos operacionais (contas de luz). Para atender às demandas do mercado, os projetistas de sistemas estão aprimorando os processos de conversão de energia em várias áreas, incluindo topologias de comutação mais eficientes, inovações de pacotes e novos dispositivos semicondutores baseados em carboneto de silício (SiC) e nitreto de gálio (GaN).

Etapa 1: Melhoria da Topologia do Conversor de Comutação

Para tirar o máximo proveito da energia disponível, as pessoas estão cada vez mais adotando projetos baseados na tecnologia de comutação em vez da tecnologia linear. A fonte de alimentação chaveada (SMPS) tem uma potência efetiva de mais de 90%. Isso estende a vida útil da bateria de sistemas portáteis, reduz o custo de eletricidade para equipamentos grandes e economiza espaço antes usado para componentes do dissipador de calor.

Alternar para uma topologia comutada tem certas desvantagens e seu design mais complexo requer que os designers tenham várias habilidades. Os engenheiros de projeto devem estar familiarizados com tecnologias analógicas e digitais, eletromagnetismo e controle de malha fechada. Os projetistas de placas de circuito impresso (PCBs) devem prestar mais atenção à interferência eletromagnética (EMI) porque as formas de onda de comutação de alta frequência podem causar problemas em circuitos analógicos e de RF sensíveis.

Antes da invenção do transistor, o conceito básico de conversão de energia comutada foi proposto: por exemplo, o sistema de descarga indutiva tipo Kate inventado em 1910, que usava um vibrador mecânico para implementar um conversor flyback boost para um sistema de ignição automotivo.

A maioria das topologias padrão existe há décadas, mas isso não significa que os engenheiros não ajustem os projetos padrão para acomodar novas aplicações, especialmente loops de controle. A arquitetura padrão usa uma frequência fixa para manter uma tensão de saída constante realimentando parte da tensão de saída (controle do modo de tensão) ou controlando a corrente induzida (controle do modo de corrente) sob diferentes condições de carga. Os designers estão constantemente se aprimorando para superar as falhas do design básico.

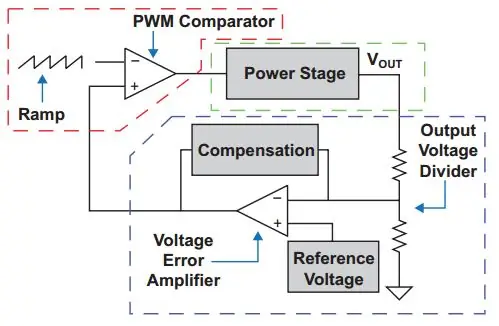

A Figura 1 é um diagrama de blocos de um sistema básico de controle de modo de tensão em malha fechada (VMC). O estágio de energia consiste em uma chave liga / desliga e um filtro de saída. O bloco de compensação inclui um divisor de voltagem de saída, um amplificador de erro, uma voltagem de referência e um componente de compensação de loop. Um modulador de largura de pulso (PWM) usa um comparador para comparar o sinal de erro a um sinal de rampa fixo para produzir uma sequência de pulso de saída que é proporcional ao sinal de erro.

Embora as diferentes cargas do sistema VMC tenham regras de saída rígidas e sejam fáceis de sincronizar com o relógio externo, a arquitetura padrão tem algumas desvantagens. A compensação de loop reduz a largura de banda do loop de controle e retarda a resposta transitória; o amplificador de erro aumenta a corrente operacional e reduz a eficiência.

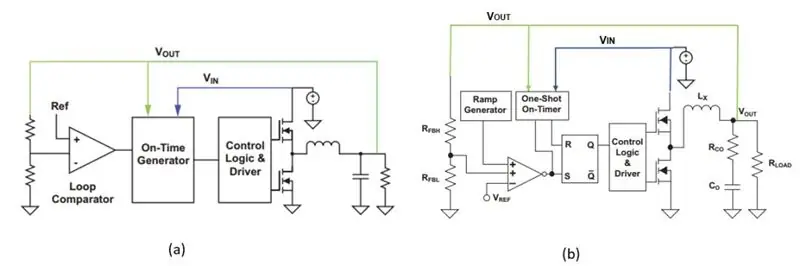

O esquema de controle constante no tempo (COT) fornece bom desempenho transiente sem compensação de loop. O controle COT usa um comparador para comparar a tensão de saída regulada com a tensão de referência: quando a tensão de saída é menor que a tensão de referência, um pulso fixo no tempo é gerado. Em ciclos de trabalho baixos, isso faz com que a frequência de chaveamento seja muito alta, de modo que o controlador COT adaptativo gera um on-time que varia com as tensões de entrada e saída, o que mantém a frequência quase constante no estado estacionário. A topologia D-CAP da Texas Instrument é uma melhoria em relação à abordagem COT adaptativa: o controlador D-CAP adiciona uma tensão de rampa à entrada do comparador de feedback, o que melhora o desempenho do jitter ao reduzir a banda de ruído no aplicativo. A Figura 2 é uma comparação dos sistemas COT e D-CAP.

Figura 2: Comparação da topologia COT padrão (a) e da topologia D-CAP (b) (Fonte: Texas Instruments) Existem diversas variantes da topologia D-CAP para diferentes necessidades. Por exemplo, o controlador PWM de meia ponte TPS53632 usa a arquitetura D-CAP +, que é usada principalmente em aplicações de alta corrente e pode gerar níveis de potência de até 1 MHz em conversores POL de 48V a 1V com eficiências de até 92%.

Ao contrário do D-CAP, o loop de feedback D-CAP + adiciona um componente que é proporcional à corrente induzida para controle de queda preciso. O amplificador de erro aumentado melhora a precisão da carga DC sob uma variedade de condições de linha e carga.

A tensão de saída do controlador é definida pelo DAC interno. Este ciclo começa quando o feedback de corrente atinge o nível de tensão de erro. Essa tensão de erro corresponde à diferença de tensão amplificada entre a tensão do ponto de ajuste do DAC e a tensão de saída de feedback.

Etapa 2: melhore o desempenho em condições de carga leve

Para dispositivos portáteis e vestíveis, é necessário melhorar o desempenho sob condições de carga leve para estender a vida útil da bateria. Muitos aplicativos portáteis e vestíveis estão em modo de espera "hibernação" ou "hibernação" de baixa energia na maior parte do tempo, ativados apenas em resposta à entrada do usuário ou medições periódicas, para minimizar o consumo de energia no modo de espera. É a maior prioridade.

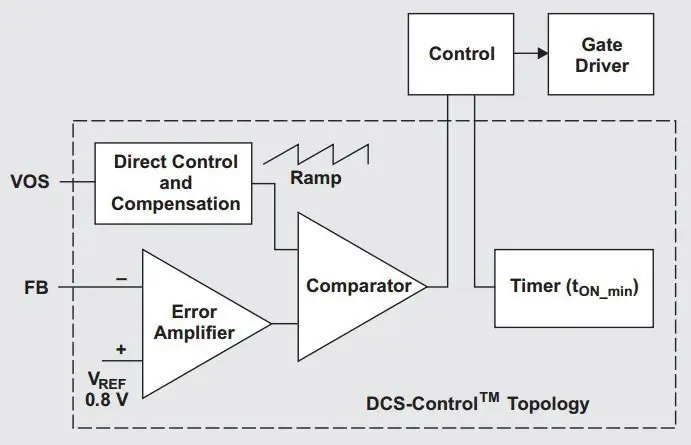

A topologia DCS-ControlTM (controle direto para transição contínua para modo de economia de energia) combina as vantagens de três esquemas de controle diferentes (ou seja, modo de histerese, modo de tensão e modo de corrente) para melhorar o desempenho sob condições de carga leve, especialmente transição para Ou quando deixando o estado de carga leve. Esta topologia suporta modos PWM para cargas médias e pesadas, bem como modo de economia de energia (PSM) para cargas leves.

Durante a operação PWM, o sistema opera em sua frequência de chaveamento nominal com base na tensão de entrada e controla a mudança de frequência. Se a corrente de carga diminuir, o conversor muda para o PSM para manter a alta eficiência até cair para uma carga muito leve. No PSM, a frequência de chaveamento diminui linearmente com a corrente de carga. Ambos os modos são controlados por um único bloco de controle, de forma que a transição de PWM para PSM seja contínua e não afete a tensão de saída.

A Figura 3 é um diagrama de blocos do DCS-ControlTM. A malha de controle obtém informações sobre a mudança na tensão de saída e as realimenta diretamente para o comparador rápido. O comparador define a frequência de chaveamento (como uma constante para condições de operação em estado estacionário) e fornece uma resposta imediata às mudanças dinâmicas de carga. O loop de feedback de tensão regula com precisão a carga CC. A rede de regulação compensada internamente permite uma operação rápida e estável com pequenos componentes externos e capacitores de baixo ESR.

Figura 3: Implementação da topologia DCS-ControlTM no conversor buck TPS62130 (Fonte: Texas Instruments)

O conversor de potência de chaveamento síncrono TPS6213xA-Q1 é baseado na topologia DCS-ControlTM e é otimizado para aplicações POL de alta densidade de potência. A frequência de comutação típica de 2,5 MHz permite o uso de pequenos indutores e fornece resposta transitória rápida e alta precisão de tensão de saída. O TPS6213 opera em uma faixa de tensão de entrada de 3 V a 17 V e pode fornecer até 3 A de corrente contínua entre as tensões de saída de 0,9 V e 6 V.

Recomendado:

Fonte de alimentação ATX oculta para fonte de alimentação de bancada: 7 etapas (com imagens)

Fonte de alimentação ATX oculta para fonte de alimentação de bancada: Uma fonte de alimentação de bancada é necessária ao trabalhar com eletrônicos, mas uma fonte de alimentação de laboratório disponível comercialmente pode ser muito cara para qualquer iniciante que queira explorar e aprender eletrônica. Mas existe uma alternativa barata e confiável. Por conve

Fonte de alimentação 220 V a 24 V 15 A - Fonte de alimentação comutada - IR2153: 8 etapas

Fonte de alimentação 220 V a 24 V 15 A | Fonte de alimentação comutada | IR2153: Oi cara, hoje. Fazemos uma fonte de alimentação de 220V a 24V 15A | Fonte de alimentação comutada | IR2153 da fonte de alimentação ATX

Como fazer uma fonte de alimentação de bancada ajustável com uma fonte de alimentação de PC antiga: 6 etapas (com fotos)

Como fazer uma fonte de alimentação de bancada ajustável com uma fonte de alimentação de PC antiga: Tenho uma fonte de alimentação de PC antiga disponível. Portanto, decidi fazer uma fonte de alimentação de bancada ajustável com ela. Precisamos de uma gama diferente de voltagens para alimentar ou verifique diferentes circuitos elétricos ou projetos. Por isso, é sempre bom ter um

Converta uma fonte de alimentação ATX em uma fonte de alimentação DC normal !: 9 etapas (com imagens)

Converta uma fonte de alimentação ATX em uma fonte de alimentação DC normal !: Uma fonte de alimentação DC pode ser difícil de encontrar e cara. Com recursos que são mais ou menos imprevisíveis para o que você precisa. Neste Instructable, vou mostrar como converter uma fonte de alimentação de computador em uma fonte de alimentação DC regular com 12, 5 e 3,3 v

Converter uma fonte de alimentação de computador em uma fonte de alimentação de laboratório de bancada variável: 3 etapas

Converta uma fonte de alimentação de computador em uma fonte de alimentação de laboratório de bancada variável: Os preços hoje para uma fonte de alimentação de laboratório ultrapassam US $ 180. Mas acontece que uma fonte de alimentação de computador obsoleta é perfeita para o trabalho. Com estes custando apenas $ 25 e tendo proteção contra curto-circuito, proteção térmica, proteção contra sobrecarga e