Índice:

- Etapa 1: Materiais

- Etapa 2: Baixe e instale o Vivado

- Etapa 3: Configurar Hardware e Restrições

- Etapa 4: definir um módulo SPI.vhd

- Etapa 5: Método de Implementação

- Etapa 6: Implementação da função de varredura WiFi

- Etapa 7: Implementação da função WiFi Connect

- Etapa 8: Transmissão de pacotes TCP / IP

- Etapa 9: Recepção de pacotes TCP / IP

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:38.

- Última modificação 2025-01-23 15:03.

Este é um Instructable para quem deseja usar um Pmod WiFi em conjunto com uma placa FPGA.

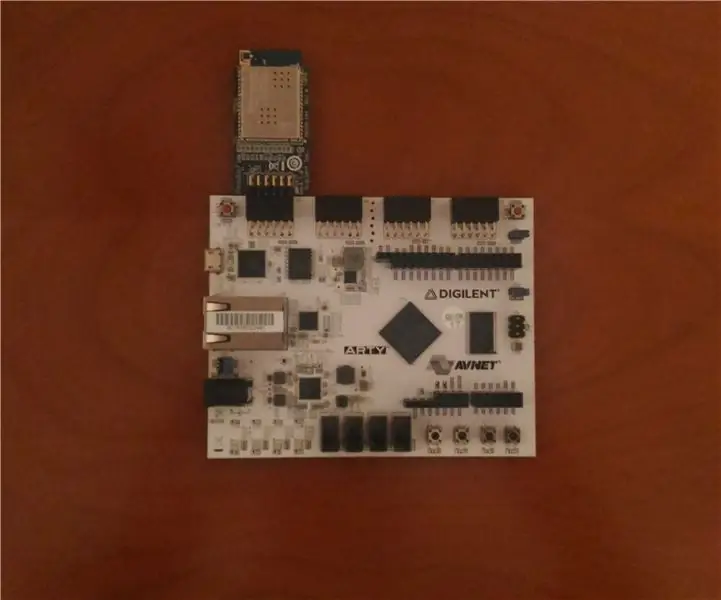

Etapa 1: Materiais

- Placa FPGA (Arty 7 neste caso)

- Pmod WiFi

- Xilinx Vivado (2016.3 neste caso)

- Roteador sem fio (para teste)

- Placa de desenvolvimento ChipKit (para teste) - Opcional

- Analisador lógico (para teste) - opcional

Etapa 2: Baixe e instale o Vivado

Um link é fornecido aqui.

Etapa 3: Configurar Hardware e Restrições

Conecte o Pmod WiFi a um conector Pmod na placa de desenvolvimento FPGA. O conector Pmod escolhido afeta o arquivo de restrições.

Defina um arquivo de restrições apropriado para sua placa FPGA (por exemplo, um arquivo.xdc para uma placa Arty). A ficha técnica do Pmod WiFi pode ser encontrada aqui.

Etapa 4: definir um módulo SPI.vhd

O Pmod WiFi usa comunicação SPI. Para estabelecer a comunicação adequada, é necessário um módulo SPI.

Etapa 5: Método de Implementação

Devido ao fato de que o Pmod WiFi não possui API para descrever suas funções, dois métodos de implementação de um driver Pmod WiFi estão disponíveis. A forma mais simples seria seguir uma API, que será descrita ao final da implementação deste projeto.

Outra maneira seria fazer a engenharia reversa de um driver preexistente, como é feito neste Instructable. Vários drivers estão disponíveis a partir de 2016, todos implementados na parte superior do microcontrolador PIC32. Para fazer a engenharia reversa de um driver preexistente, será necessário um microcontrolador PIC32 (uma placa ChipKit neste caso) e um analisador lógico.

Uma breve descrição dos registros MRF24WG pode ser encontrada aqui.

Uma demonstração em vídeo de uma captura de comunicação ChipKit Pmod WiFi pode ser encontrada aqui.

Etapa 6: Implementação da função de varredura WiFi

A função de varredura de WiFi verifica as redes WiFi disponíveis e as transmite para o host. Esta é a primeira etapa necessária para se conectar a uma rede e iniciar a comunicação.

Etapa 7: Implementação da função WiFi Connect

A função de conexão WiFi estabelece uma conexão - aberta (sem segurança) ou segura (por exemplo, WPA2) entre o Pmod WiFi e um roteador sem fio. Outros parâmetros significativos são representados por um SSID e um tipo de rede (infra-estrutura ou ad-hoc).

Etapa 8: Transmissão de pacotes TCP / IP

Uma transmissão de pacote TCP / IP requer um soquete de destino (endereço IP e porta TCP). Uma transmissão TCP / IP só pode ser realizada após o estabelecimento bem-sucedido de uma conexão.

Etapa 9: Recepção de pacotes TCP / IP

Para receber com sucesso um pacote TCP / IP, é necessário abrir um soquete no host.

Recomendado:

FPGA Cyclone IV DueProLogic controla a câmera Raspberry Pi: 5 etapas

FPGA Cyclone IV DueProLogic Controla Câmera Raspberry Pi: Apesar do FPGA DueProLogic ser oficialmente projetado para Arduino, vamos tornar o FPGA e o Raspberry Pi 4B comunicáveis. Três tarefas são implementadas neste tutorial: (A) Pressione simultaneamente os dois botões em FPGA para inverter o ângulo de

FPGA Cyclone IV DueProLogic - Botão e LED: 5 etapas

FPGA Cyclone IV DueProLogic - Botão e LED: Neste tutorial, vamos usar o FPGA para controlar o circuito de LED externo. Vamos implementar as seguintes tarefas (A) Use os botões de pressão no FPGA Cyclone IV DuePrologic para controlar o LED. (B) Flash LED no & desligado periodicamenteLaboratório de demonstração de vídeo

Servo motor FPGA Cyclone IV DueProLogic: 4 etapas

FPGA Cyclone IV DueProLogic Controles Servo Motor: Neste tutorial, vamos escrever código Verilog para controlar o servo motor. O servo SG-90 é fabricado pela Waveshare. Ao comprar o servo motor, você pode receber uma folha de dados que lista a tensão de operação, o torque máximo e o Pu proposto

Esteira DIY VR - Concurso Basys3 FPGA-Digilent: 3 etapas

DIY VR Treadmill- Basys3 FPGA-Digilent Contest: Você quer construir uma esteira VR na qual você possa executar seus aplicativos e jogos de desktop? Então você veio ao lugar certo! Nos jogos convencionais você usa o mouse e o teclado para interagir com o ambiente. Portanto, precisamos enviar o

Mojo FPGA Development Board Shield: 3 etapas

Mojo FPGA Development Board Shield: Conecte sua placa de desenvolvimento Mojo a entradas externas com este escudo. O que é a placa de desenvolvimento Mojo? A placa de desenvolvimento Mojo é uma placa de desenvolvimento baseada no Xilinx spartan 3 FPGA. O tabuleiro é feito pela Alchitry. FPGAs são muito úteis