Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:35.

- Última modificação 2025-01-23 15:03.

Neste tutorial, vamos escrever código Verilog para controlar servo motor. O servo SG-90 é fabricado pela Waveshare. Ao comprar o servo motor, você pode receber uma folha de dados que lista a tensão de operação, o torque máximo e a modulação por largura de pulso (PWM) proposta … etc. No entanto, o FPGA DuePrologic fornece tensão de entrada de 3,3 V onde a tensão de operação do servo SG-90 é 5 V - 7 V. Na falta de energia elétrica, listarei meu PWM calibrado para girar o servo motor com sucesso.

Nossa tarefa: O servo motor é girado para frente e para trás com o período de 5 segundos

Menu completo:

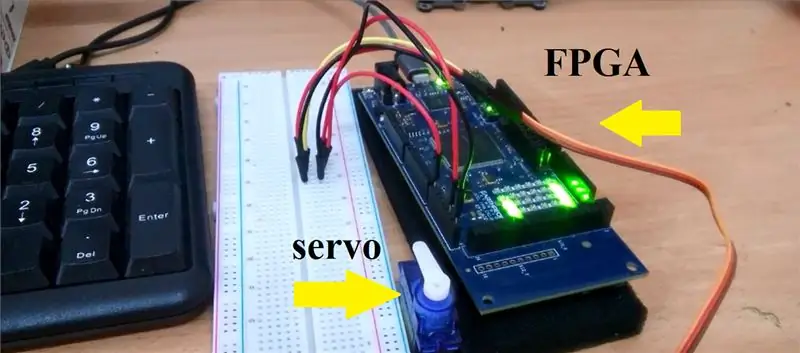

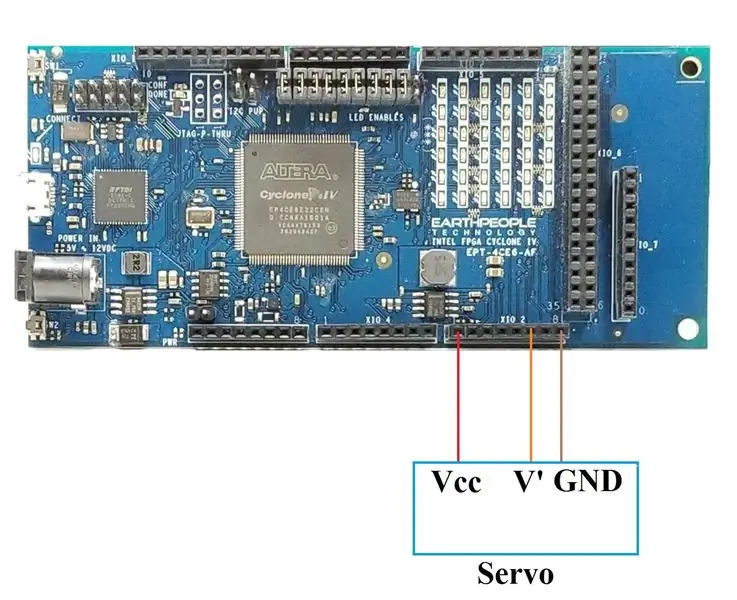

Etapa 1: construir o circuito eletrônico

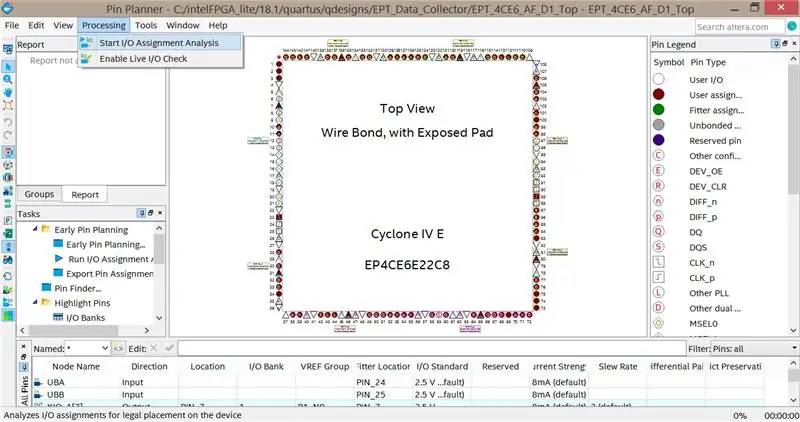

Etapa 2: configurar o planejador de pinos

Clique em "Iniciar Análise de Atribuição de E / S" para verificar se o planejador de pinos está configurado corretamente. Caso contrário, você terá que importar todos os nomes de portas por conta própria.

Etapa 3: Código Verilog

Criamos um temporizador "servo_count". Quando "servo_A" é HIGH, o PWM é 1,5 ms e, portanto, o servo está localizado a 120 graus. Em contraste, quando "servo_A" é BAIXO, o PWM é 0,15 ms e, portanto, o servo é mantido em 0 grau.

atribuir XIO_2 [3] = servo_pulse; // para V '

reg [31: 0] servo_count;

começo inicial

servo_count <= 32'b0;

servo_A <= 1'b0;

fim

sempre @ (posedge CLK_66)

começar

servo_count <= servo_count + 1'b1;

if (servo_count> 400000000) // Ciclo do relógio 66MHz, 1 / 66M * 400000000 ~ 5 segundos

começar

servo_A <=! servo_A;

servo_count <= 32'b0;

fim

fim

reg [31: 0] ex_auto;

começo inicial

ex_auto <= 32'b0;

servo_auto <= 1'b0;

fim

sempre @ (posedge CLK_66)

começar

if (servo_A == 1'b1)

começar

ex_auto <= ex_auto + 1'b1;

if (ex_auto> 100000) // Ciclo de clock de 66 MHz, este PWM é ~ 1,5 ms, o servo gira para 120 graus

começar

servo_auto <=! servo_auto;

ex_auto <= 32'b0;

fim

fim

if (servo_A == 1'b0)

começar

ex_auto <= ex_auto + 1'b1;

if (ex_auto> 10000) // Ciclo de clock de 66 MHz, este PWM é ~ 0,15 ms, o servo gira para 0 graus

começar

servo_auto <=! servo_auto;

ex_auto <= 32'b0;

fim

fim

fim

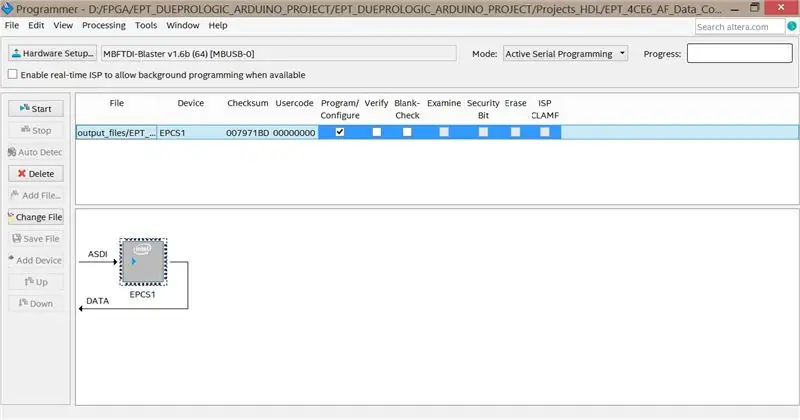

Etapa 4: fazer upload do código Verilog

Clique em "Iniciar Compilação". Se nenhuma mensagem de erro for exibida, vá para "Programador" para concluir a configuração do hardware. Lembre-se de atualizar o arquivo pof em "Alterar arquivo" se necessário. Clique em "Iniciar" para fazer o upload do código.

Afinal, você deve ver que o servo motor é girado periodicamente.

Recomendado:

FPGA Cyclone IV DueProLogic controla a câmera Raspberry Pi: 5 etapas

FPGA Cyclone IV DueProLogic Controla Câmera Raspberry Pi: Apesar do FPGA DueProLogic ser oficialmente projetado para Arduino, vamos tornar o FPGA e o Raspberry Pi 4B comunicáveis. Três tarefas são implementadas neste tutorial: (A) Pressione simultaneamente os dois botões em FPGA para inverter o ângulo de

FPGA Cyclone IV DueProLogic - Botão e LED: 5 etapas

FPGA Cyclone IV DueProLogic - Botão e LED: Neste tutorial, vamos usar o FPGA para controlar o circuito de LED externo. Vamos implementar as seguintes tarefas (A) Use os botões de pressão no FPGA Cyclone IV DuePrologic para controlar o LED. (B) Flash LED no & desligado periodicamenteLaboratório de demonstração de vídeo

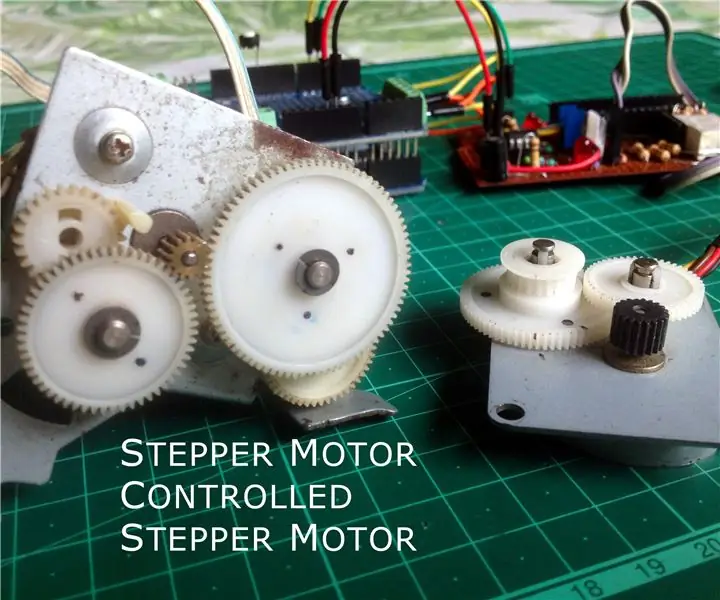

Motor de passo controlado por motor de passo - Motor de passo como codificador giratório: 11 etapas (com imagens)

Motor de passo controlado por motor de passo | Motor de passo como codificador rotativo: Você tem alguns motores de passo por aí e quer fazer alguma coisa? Neste Instructable, vamos usar um motor de passo como um codificador rotativo para controlar a posição de outro motor de passo usando um microcontrolador Arduino. Então, sem mais delongas, vamos

Como executar o motor DC sem escova Drone Quadcopter usando o controlador de velocidade do motor sem escova HW30A e o servo testador: 3 etapas

Como executar o motor DC sem escova Drone Quadcopter usando o controlador de velocidade do motor sem escova HW30A e servo testador: Descrição: este dispositivo é chamado de testador de servo motor, que pode ser usado para executar o servo motor por simples plug no servo motor e fonte de alimentação para ele. O dispositivo também pode ser usado como um gerador de sinal para controlador elétrico de velocidade (ESC), então você não pode

Braço do robô servo motor RC controlado por Fpga - Concurso Digilent: 3 etapas

Braço de robô servo motor RC controlado por Fpga - Concurso Digilent: braço de robô servo motor controlado por FPGA. O objetivo deste projeto é criar um sistema programável que possa realizar operações de soldagem na placa perf. O sistema é baseado na placa de desenvolvimento Digilent Basys3 e será capaz de soldar co