Índice:

- Etapa 1: O que é Vivado HLS?

- Etapa 2: Biblioteca de vídeo HLS

- Etapa 3: Sintetizando

- Etapa 4: controle de versão e outras informações para exportação

- Etapa 5: Exportando para uma biblioteca Vivado IP

- Etapa 6: Análise de Síntese e Exportação

- Etapa 7: Adicionando a Biblioteca IP no Vivado

- Etapa 8: fazer um upgrade

- Etapa 9: detalhes e informações adicionais

- Etapa 10: saída e entrada

- Etapa 11: Interface de registro AXI

- Etapa 12: Dataflow Pragma

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:39.

- Última modificação 2025-01-23 15:03.

Você sempre quis processar vídeo em tempo real sem adicionar muita latência ou em um sistema integrado? FPGAs (Field Programmable Gate Arrays) às vezes são usados para fazer isso; no entanto, escrever algoritmos de processamento de vídeo em linguagens de especificação de hardware como VHDL ou Verilog é, na melhor das hipóteses, frustrante. Digite Vivado HLS, a ferramenta Xilinx que permite programar em um ambiente C ++ e gerar código de linguagem de especificação de hardware a partir dele.

Softwares necessários:

- Vivado HLS

- Vivado

- (Se você usar os registros AXI) Vivado SDK

(Opcional) Baixe os exemplos feitos pelo Xilinx aqui:

Exemplos de vídeo Xilinx HLS

Etapa 1: O que é Vivado HLS?

Vivado HLS é uma ferramenta usada para transformar o código c ++ em estruturas de hardware que podem ser implementadas em um FPGA. Inclui um IDE para fazer este desenvolvimento. Depois de concluir o desenvolvimento do código para HLS, você pode exportar o IP gerado em um formato para uso com Vivado.

Baixe os arquivos anexados e coloque-os perto de onde você criará seu projeto. (renomeie-os de volta para "top.cpp" e "top.h" se eles tiverem um nome aleatório)

Etapa 2: Biblioteca de vídeo HLS

A HLS Video Library tem documentação com designs de referência neste artigo: XAPP1167 Outro bom recurso é a página Wiki do Xilinx sobre o assunto.

Inicie o Vivado HLS.

Crie um novo projeto.

Pegue os arquivos que você baixou na etapa anterior e adicione-os como arquivos de origem. (Observação: os arquivos não são copiados para o projeto, mas permanecem onde estão)

Em seguida, use o botão Navegar para selecionar a função superior.

Na próxima página, selecione a peça Xilinx que você está usando.

Etapa 3: Sintetizando

Solução => Executar Síntese C => Solução Ativa

Depois de aproximadamente 227,218 segundos, isso deve ser feito. (Nota: o seu tempo de síntese real irá variar com base em muitos fatores)

Etapa 4: controle de versão e outras informações para exportação

Os números de versão interagem com o Vivado para permitir que você atualize o IP em um design. Se for uma alteração de versão secundária, isso pode ser feito no local enquanto as alterações de versão principais exigem que você adicione manualmente o novo bloco e remova o antigo. Se suas interfaces não foram alteradas e a atualização da versão é secundária, a atualização pode ser feito de forma totalmente automática, pressionando o botão de atualização de IP. Você pode executar "report_ip_status" no console tcl do Vivado para ver o status do seu IP.

Defina os números da versão e outras informações em Solução => Configurações da solução …

Como alternativa, essas configurações podem ser definidas durante a exportação.

Etapa 5: Exportando para uma biblioteca Vivado IP

Solução => Exportar RTL

Se você não configurou os detalhes da biblioteca de IP na etapa anterior, pode fazer isso agora.

Etapa 6: Análise de Síntese e Exportação

Nesta tela podemos ver as estatísticas sobre nosso módulo exportado, mostrando que ele cumpre nosso período de clock de 10ns (100MHz) e quanto de cada recurso ele usa.

Com uma combinação disso, nosso relatório de síntese e nossa análise de fluxo de dados, podemos ver que leva 317.338 ciclos de relógio * período de 10 ns * 14 estágios de pipeline = 0,04442732 segundos. O que significa que a latência total adicionada pelo nosso processamento de imagem é inferior a um vigésimo de segundo (quando cronometrado no alvo de 100 MHz).

Etapa 7: Adicionando a Biblioteca IP no Vivado

Para usar seu bloco de IP sintetizado, você precisará adicioná-lo ao Vivado.

No Vivado, adicione um repositório de IP ao seu projeto indo ao catálogo de IP e clique com o botão direito e selecionando "Adicionar Repositório …"

Navegue até o diretório do projeto Vivado HLS e selecione o diretório da solução.

Ele deve relatar o IP que encontrou.

Etapa 8: fazer um upgrade

Às vezes, você precisa fazer alterações em seu bloco HLS após incluí-lo em um design Vivado.

Para fazer isso, você pode fazer as alterações e ressintetizar e exportar o IP com um número de versão superior (consulte os detalhes na etapa anterior sobre alterações de número de versão principal / secundária).

Após alterar a exportação da nova versão, atualize seus repositórios IP no Vivado. Isso pode ser feito quando o Vivado percebe que o IP mudou no repositório, ou pode ser ativado manualmente. (Observe, se você atualizar seus repositórios de IP após o início, mas antes que a exportação seja concluída em HLS, o IP temporariamente não estará lá, espere que ele termine e atualize novamente.)

Neste ponto, uma janela deve aparecer com a informação de que um IP foi alterado no disco e dá a você a opção de atualizá-lo com um botão "Upgrade Selecionado". Se a mudança foi uma pequena mudança de versão e nenhuma das interfaces mudou, em seguida, pressionar esse botão substituirá automaticamente o IP antigo pelo novo, caso contrário, mais trabalho pode ser necessário.

Etapa 9: detalhes e informações adicionais

As etapas a seguir fornecem mais informações sobre como funciona a síntese HLS e o que você pode fazer com ela.

Para obter um exemplo de um projeto usando um bloco IP sintetizado por HLS, consulte este instrutível.

Etapa 10: saída e entrada

Saídas e entradas para o bloco IP final são determinadas a partir de uma análise que o sintetizador faz do fluxo de dados de entrada e saída da função superior.

Semelhante ao VHDL ou verilog, o HLS permite que você especifique detalhes sobre as conexões entre IP. Essas linhas são exemplos disso:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma Porta do eixo HLS INTERFACE = video_in bundle = INPUT_STREAM #pragma Porta do eixo HLS INTERFACE = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE porta s_axilite = x bundle = CONTROL_BUS offset = 0x14 # pragma HLS INTERFACE s_axilite porta 0xC

Você pode ver como as portas exibidas no bloco IP são influenciadas por essas diretivas.

Etapa 11: Interface de registro AXI

Para obter entrada / saída de / para seu bloco de IP para o PS, uma boa maneira de fazer isso é por meio de uma interface AXI.

Você pode especificar isso em seu código HLS, incluindo os deslocamentos a serem usados para acessar o valor posteriormente, como este:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite porta = x pacote = CONTROL_BUS deslocamento = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

Uma vez conectado corretamente no Vivado, você pode acessar os valores usando este código no Vivado SDK:

#include "parameters.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR + xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR + yregoff);

Isso fará com que você termine com 42 em xe 0xdeadbeef em y

Etapa 12: Dataflow Pragma

Dentro do #pragma DATAFLOW a forma como o código é implementado muda do C ++ normal. O código é canalizado para que todas as instruções sejam executadas em todos os momentos em diferentes partes dos dados (pense nisso como uma linha de montagem em uma fábrica, cada estação está trabalhando continuamente fazendo uma função e passando para a próxima estação)

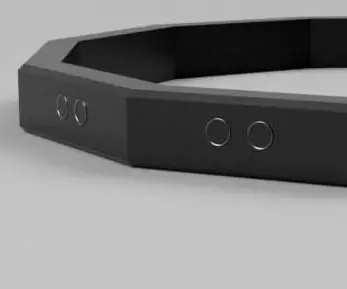

na imagem você pode ver que cada uma das diretivas

Apesar de parecerem ser variáveis normais, os objetos img são, na verdade, implementados como pequenos buffers entre os comandos. Usar uma imagem como entrada para uma função a "consome" e a torna inutilizável. (Daí a necessidade de comandos duplicados)

Recomendado:

Motor de passo controlado por MIDI com chip de síntese digital direta (DDS): 3 etapas

Motor de passo controlado por MIDI com chip de síntese digital direta (DDS): Você já teve a má idéia de que SÓ teve que se transformar em um miniprojeto? Bem, eu estava brincando com um esboço que fiz para o Arduino Due com o objetivo de fazer música com um módulo AD9833 Direct Digital Synthesis (DDS) … e em algum momento pensei & q

Minha primeira síntese: 29 etapas (com imagens)

Meu primeiro sintetizador: o sintetizador infantil surgiu enquanto eu me sentava curvado sobre uma confusão emaranhada de fios de sintetizador. Meu amigo Oliver se aproximou, avaliou a situação e disse: "Você sabe que conseguiu fazer o brinquedo infantil mais complicado do mundo". Enquanto meu r inicial

Módulo de síntese Raspberry Pi Stompbox: 6 etapas (com imagens)

Módulo Raspberry Pi Stompbox Synth: O objetivo deste projeto é colocar um módulo de som baseado em Fluidsynth em um stompbox. O termo de aparência técnica " módulo de som " neste caso, significa um dispositivo que recebe mensagens MIDI (ou seja, valor da nota, volume, pitch bend, etc.) e sintetizadores

Phono-Chronoxyle - uma síntese de 360 graus: 3 etapas (com imagens)

Phono-Chronoxyle - um sintetizador de 360 graus: o escultor Julien Signolet residente em Paris e o músico Mathias Durand me abordaram para uma instalação sonora interativa no Parc Floral em Paris para Nuit Blanche 2019. A instalação seria ao ar livre e eu não estaria presente durante o em

Síntese de som analógico em seu computador: 10 etapas (com imagens)

Síntese de som analógico em seu computador: Gosta do som daqueles antigos sintetizadores analógicos? Quer jogar com um no seu tempo, em sua casa, pelo tempo que quiser, de GRAÇA? É aqui que seus sonhos mais loucos de Moog se tornam realidade. Você pode se tornar um artista de gravação eletrônica ou apenas