Índice:

- Etapa 1: Operação do usuário do sequenciador digital

- Etapa 2: detalhes técnicos

- Etapa 3: detalhes técnicos

- Etapa 4: divisor de relógio de 7 segmentos

- Etapa 5: divisor de batidas por minuto

- Etapa 6: Divisor de relógio de pitches

- Etapa 7: Reproduzir / pausar / selecionar máquina de estado

- Etapa 8: Reproduzir / pausar / selecionar máquina de estado

- Etapa 9: Saída FSM

- Etapa 10: Saída FSM

- Etapa 11: atribuição de nota

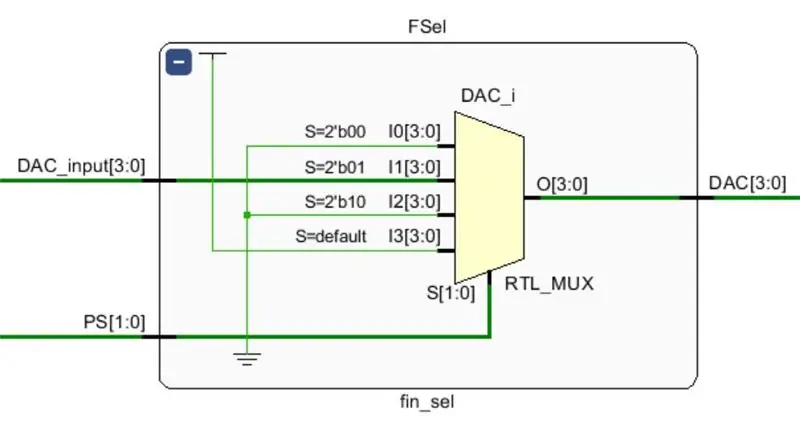

- Etapa 12: Seleção de saída

- Etapa 13: Square Wave Gen

- Etapa 14: display de 7 segmentos

- Etapa 15: Seleção final

- Etapa 16: Dispositivos externos: DAC

- Etapa 17: Dispositivos Externos: Alto-falante

- Etapa 18: Demonstração em vídeo

- Etapa 19: Código VHDL

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:39.

- Última modificação 2025-01-23 15:03.

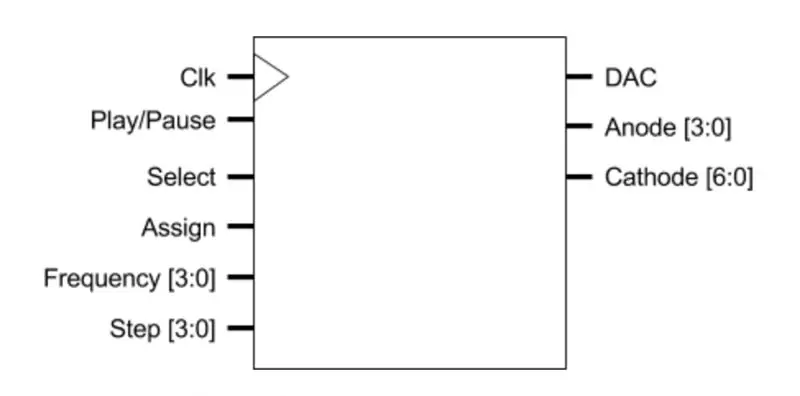

CPE 133, Cal Poly San Luis Obispo

Criadores do projeto: Jayson Johnston e Bjorn Nelson

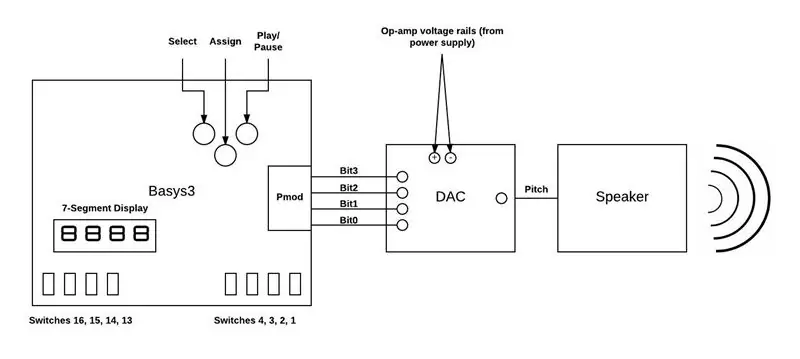

Na indústria da música de hoje, um dos “instrumentos” mais comumente usados é o sintetizador digital. Todos os gêneros musicais, do hip-hop ao pop e até mesmo country, usam um sintetizador digital no estúdio para criar as batidas e os sons de que precisam para dar vida à música. Neste tutorial, iremos criar um sintetizador muito simples com a placa Basys 3 FPGA.

O sintetizador será capaz de tocar quatro semínimas selecionadas em um número constante de batidas por minuto. Os usuários usarão os interruptores para atribuir cada semínima a um tom musical. Para este projeto, estamos usando um conversor digital para analógico (DAC) de 4 bits para pegar a saída da placa e convertê-la em um sinal analógico. A saída do DAC será então enviada para um alto-falante padrão do computador, criando nossa música. Dezesseis passos discretos são possíveis. Vamos restringir nosso sintetizador a uma única oitava de 12 notas, que ficam entre o dó médio (261,6 Hz) e B4 (493,9 Hz). O usuário também terá a opção de atribuir várias notas ao mesmo tempo, bem como atribuir uma pausa clicando em atribuir sem ter nenhum dos interruptores de afinação deslocados para cima. À medida que cada nota é selecionada e tocada, a letra da nota é exibida no visor de 7 segmentos. Também usaremos três dos botões no quadro, um para tocar e pausar a música, um para redefinir o sintetizador e colocá-lo no modo de “seleção” e o terceiro para atribuir a cada nota uma altura no modo de seleção.

Quando o usuário estiver satisfeito com a escolha das notas e depois de pressionar o botão play, o sintetizador tocará cada nota em sucessão repetidamente até que o usuário pressione pause ou selecione.

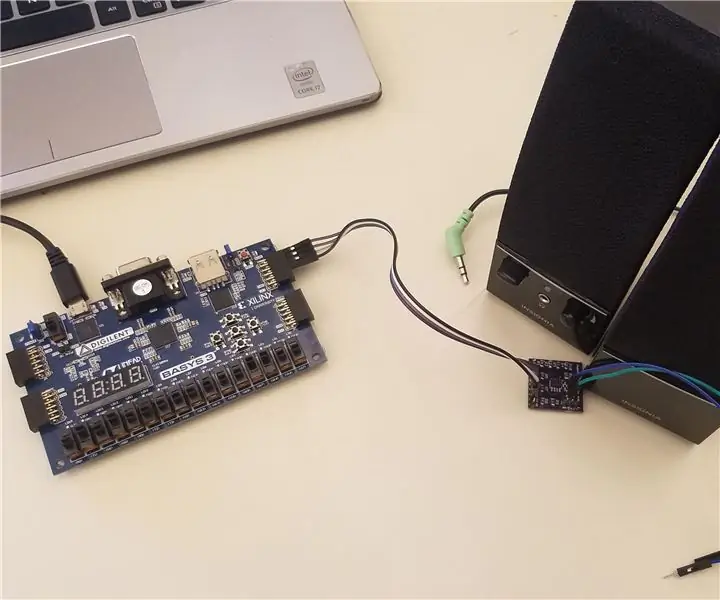

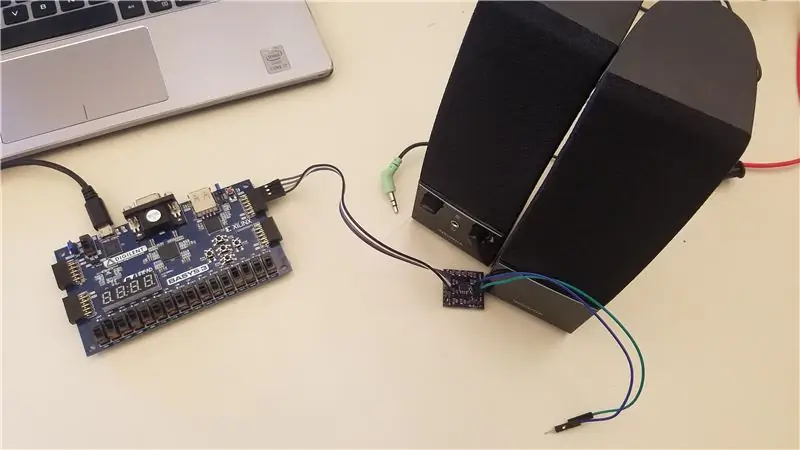

Aqui está uma lista dos equipamentos necessários:

- Vivado (ou qualquer espaço de trabalho VHDL)

- Basys 3 ou placa FPGA semelhante

- Conversor digital para analógico (mín. 4 bits)

- Alto-falante com entrada para fone de ouvido

- Cabos de fios

Etapa 1: Operação do usuário do sequenciador digital

As etapas a seguir são para operar o sequenciador digital. O sequenciador digital suporta a reprodução de 12 tons distintos (C, Db, Ré, Eb, E, F, Gb, G, Ab, A, Bb, B), que variam de 261,6 Hz a 493,9 Hz.

1. Pressione o botão esquerdo para colocar o painel no modo de seleção. Quando neste modo, os 4 interruptores mais à esquerda (interruptores 13 a 16) serão usados cada um para armazenar um valor de afinação distinto.

2. Para fazer uma seleção, ligue um dos interruptores à esquerda e, em seguida, use os 4 interruptores mais à direita (interruptores 1 a 4) para escolher a afinação desejada. O tom associado a uma combinação específica de interruptores certos será mostrado no display de sete segmentos, e o display será atualizado para o novo pitch associado sempre que os interruptores certos forem mudados para uma nova combinação. Uma pausa pode ser atribuída nunca atribuindo uma afinação a um dos interruptores esquerdos ou atribuindo à nota uma afinação mostrada como 0 no visor. Depois que a afinação desejada for encontrada e exibida no visor, pressione o botão de atribuição inferior para atribuir essa afinação específica à nota.

3. Repita a etapa 2 para as três notas restantes, virando cada uma das chaves restantes da esquerda individualmente, escolhendo a respectiva afinação com as chaves da direita e pressionando o botão inferior para atribuir a afinação à nota. Várias notas podem ser atribuídas ao mesmo tom, deslocando mais de um dos interruptores da esquerda para cima ao mesmo tempo.

4. Agora que todas as afinações das notas foram atribuídas, o sequenciador digital está pronto para tocar. Para tocar as notas no alto-falante, basta pressionar o botão direito reproduzir / pausar para iniciar a reprodução da música. A ordem da sequência de reprodução reflete os tons associados aos interruptores da esquerda, da esquerda para a direita. As notas serão tocadas em um determinado número de batidas por minuto, na ordem 1, 2, 3, 4, 1, 2…. O visor mostrará a nota que está tocando no momento enquanto os alto-falantes tocam a música. Para pausar a reprodução da música, basta pressionar o botão direito e, em seguida, a música irá parar de tocar e um símbolo de pausa será mostrado no visor. Pressione o botão direito novamente para retomar a reprodução.

Etapa 2: detalhes técnicos

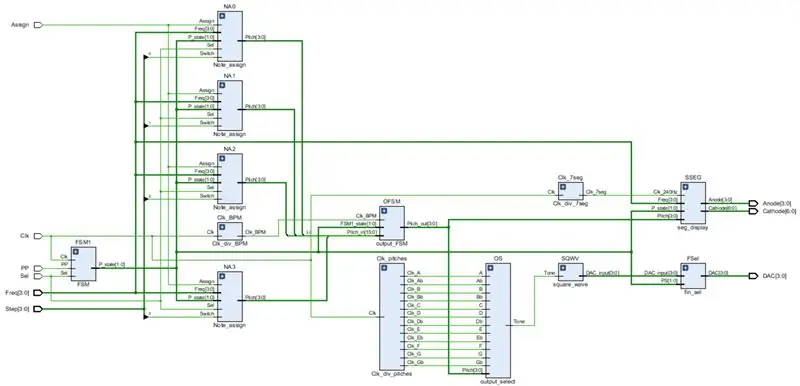

Nosso sintetizador usa muitos componentes digitais diferentes. Estão incluídos máquinas de estado finito, registradores, multiplexadores, divisores de relógio e muito mais. Para construir nosso sintetizador, usamos 10 arquivos modulares exclusivos. Em vez de tornar cada módulo um componente, dividimos os arquivos modulares por função. Como resultado, a maioria dos módulos é mais de um componente. Observe que a imagem acima mostra todos os blocos amarrados em nosso design superior.

Discutiremos cada módulo descrevendo as entradas e saídas, dividindo seus componentes e explicando sua finalidade no design geral. Um arquivo ZIP está incluído na parte inferior do instrutível, que contém todos os arquivos de código VHDL usados no projeto.

Entradas

- Clk (sinal de relógio nativo)

- PP (reproduzir / pausar)

- Sel (colocar o sintetizador no modo de seleção)

- Atribuir (atribuir uma etapa a um argumento de venda)

- Etapa (as notas posicionais)

- Freq (os interruptores criando a afinação desejada)

Saídas

- Ânodo (ânodos de 7 segmentos)

- Cátodo (cátodos de 7 segmentos)

- DAC (4 bits conduzindo o DAC)

Etapa 3: detalhes técnicos

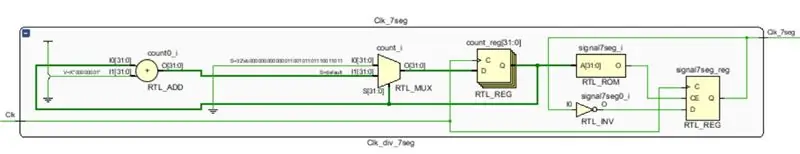

Etapa 4: divisor de relógio de 7 segmentos

Nosso sintetizador faz uso de três divisores de clock, todos produzindo sinais que servem a um propósito diferente em nosso projeto. Um divisor de relógio pega um sinal de relógio nativo e produz um sinal alterado que tem uma frequência menor do que o sinal de relógio original. O clock nativo do Basys 3 é 100 MHz. Esta é a frequência que nossos divisores de relógio utilizam. Se você estiver usando uma placa FPGA diferente com uma frequência de clock nativa diferente, pode ser necessário alterar o código.

O divisor de clock de 7 segmentos produz um sinal que conduz o arquivo seg_display. Explicaremos como esse arquivo funciona com mais detalhes quando chegarmos à sua seção. Essencialmente, este divisor de clock produz um sinal de 240 Hz que será usado para alternar entre ânodos e cátodos no display. O sinal é 240 Hz porque a frequência na qual o olho humano não consegue reconhecer a ausência de luz é 60 Hz. Estamos usando dois dígitos, portanto, ao dobrar essa frequência, cada dígito oscilará a 60 Hz. Então dobramos para chegar a 240 Hz porque o sistema só muda quando o sinal fica alto, não quando fica baixo.

Para conseguir isso, o divisor pega o sinal nativo de 100 MHz e faz a contagem progressiva em cada borda de subida. Quando o contador atinge 416667, a saída irá de baixa para alta ou vice-versa.

Entradas

Clk (sinal de relógio nativo)

Saídas

Clk_7seg (para seg_display)

Componentes

- Registro D

- MUX

- Inversor

- Adicionador

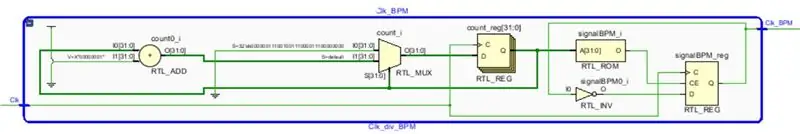

Etapa 5: divisor de batidas por minuto

O divisor de clock do BPM funciona de maneira semelhante. Este divisor produz a frequência do clock que conduz a alternância entre as quatro etapas ao emitir tons no estado de reprodução. Decidimos alternar entre as notas a 100 BPM. A 100 BPM, cada nota será tocada por 3/5 de segundo. O sinal resultante teria uma frequência de 1,67 Hz.

Para produzir um sinal desta frequência, usamos novamente um sistema de contagem, mas desta vez a contagem foi de 60 milhões. Cada vez que o contador atingia 60 milhões, o sinal de saída mudava para alto ou baixo.

Entradas

Clk (frequência de relógio nativa)

Saídas

Clk_BPM (para output_FSM)

Componentes

- Registro D

- MUX

- Inversor

- Adicionador

Etapa 6: Divisor de relógio de pitches

O Pitches Clock Divider é o maior dos nossos divisores de relógio. Este divisor emite 12 sinais diferentes correspondentes às 12 notas diferentes que nosso sintetizador pode tocar. Usando conhecimentos básicos de teoria musical, deduzimos que um bit ou barramento pode oscilar a uma taxa que corresponde à frequência das notas musicais. Para ver as frequências que usamos, veja aqui. Usamos a quarta oitava das notas.

O mesmo sistema de contagem é usado aqui. Para os valores específicos com os quais contamos, consulte o arquivo denominado Clk_div_pitches.

Entradas

Clk (frequência de relógio nativa)

Saídas

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (para output_select)

Componentes

- Registro D

- MUX

- Inversor

- Adicionador

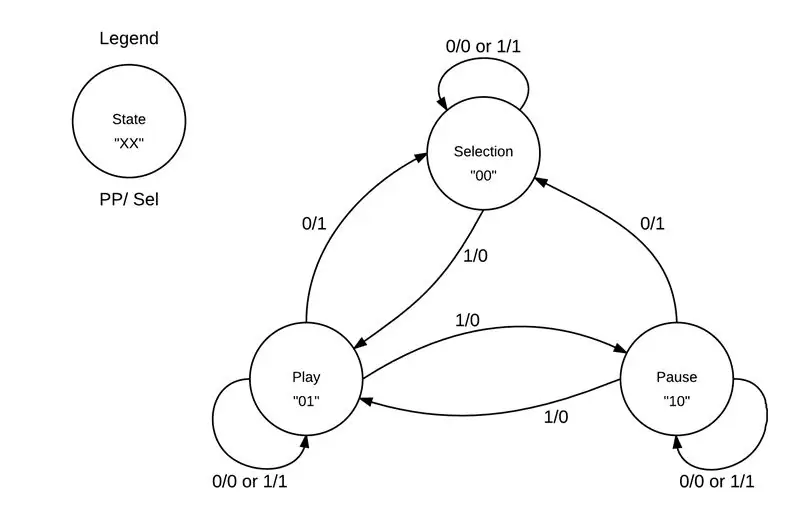

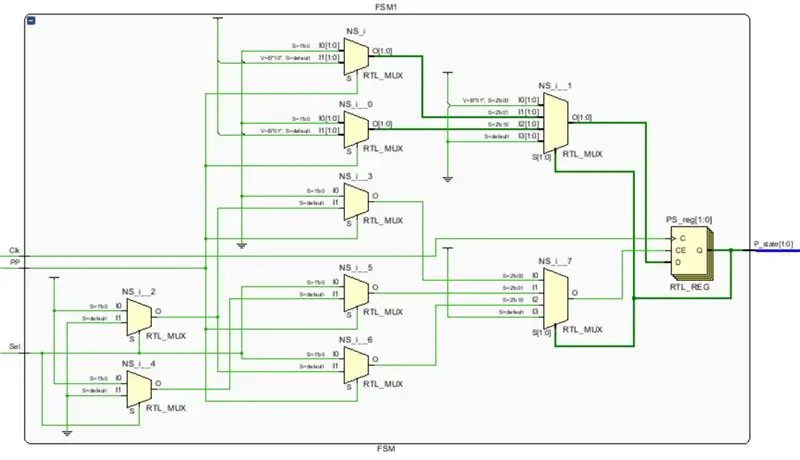

Etapa 7: Reproduzir / pausar / selecionar máquina de estado

Em nosso projeto, existem duas máquinas de estado finito (FSM). Um FSM é um dispositivo lógico que pode existir em apenas um estado entre uma quantidade finita de estados. Usando um FSM, um circuito digital pode passar para um novo estado com base em uma combinação de entradas. Usando a lógica de entrada, o estado de um FSM mudará quando houver uma transição positiva do relógio. A partir do estado e das entradas no circuito, você pode criar uma lógica de saída que fornece saídas que só existem se o FSM estiver em um determinado estado.

A máquina de estado PPS é o primeiro FSM em nosso circuito. Existem três estados neste FSM; Modo de reprodução, pausa e seleção. Para percorrer os diferentes estados, usamos os botões PP e Seleção. Consulte o diagrama de estado acima para ver como ocorrem as transições entre os estados. Fizemos essa transição FSM na borda ascendente do clock nativo de 100 MHz, de modo que seria impossível para a máquina não fazer a transição quando um dos botões fosse pressionado, mesmo por um período de tempo muito curto. O estado atual (P_state) é a única saída deste módulo.

Entradas

- Clk (frequência de relógio nativa)

- Sel (botão esquerdo)

- PP (botão direito)

Saídas

P_state (estado atual, para output_FSM, note_assign, seg_dsiplay, final_select)

Componentes

- MUX

- Registro D

Etapa 8: Reproduzir / pausar / selecionar máquina de estado

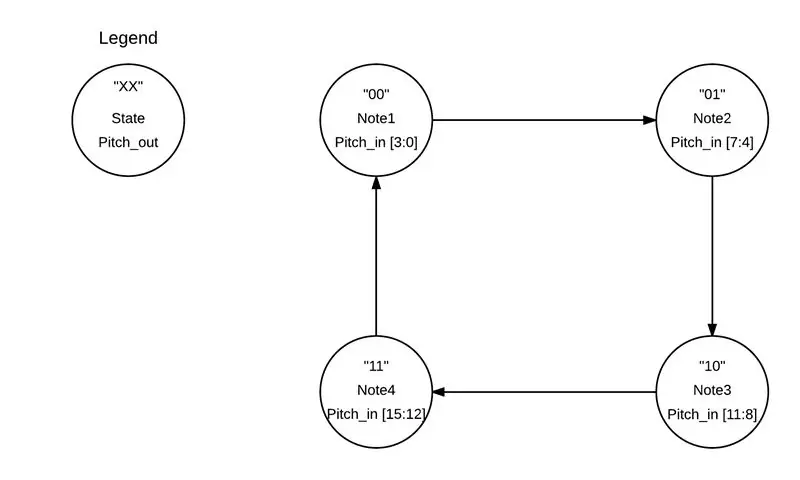

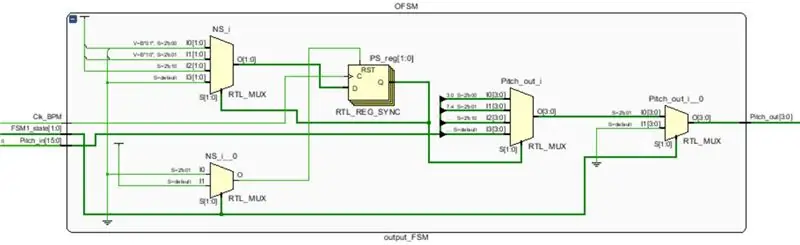

Etapa 9: Saída FSM

Este é o segundo FSM referenciado na seção anterior. Este FSM tem uma função diferente do outro, mas a base para este é essencialmente a mesma.

A saída FSM só opera se o estado atual do primeiro FSM for "01" (o estado de reprodução). Essencialmente, é a entrada de ativação do módulo. Se o estado for "01", o FSM irá alternar entre os estados na borda ascendente do sinal de clock BPM. Fazemos isso porque o output_FSM está controlando qual número binário para o pitch selecionado é enviado para os módulos output_select e seg_display. O FSM tem uma entrada de 16 bits proveniente do módulo de atribuição de notas, que será abordado a seguir. No estado "00" para output_FSM, o módulo emitirá "xxxx" para a primeira nota atribuída. Em seguida, em "01", a saída será "yyyy" para a segunda nota e assim por diante para cada nota antes de voltar para a primeira nota. Veja o diagrama de estado acima.

Este FSM difere do primeiro porque não há lógica de entrada para controlar a comutação entre os estados. Em vez disso, o FSM só vai operar quando o estado do primeiro FSM for "01" e, então, esse FSM fará a transição entre os estados apenas na transição ascendente do sinal de clock. Outra diferença é que este módulo possui lógica de saída, o que significa que ele não produz o estado atual, mas sim o número binário da afinação naquele estado.

Entradas

- Clk_BPM (sinal de relógio BPM do divisor de relógio)

- FSM1_state (PS de PPS FSM)

- Pitch_in (arremessos de note_assign)

Saídas

Pitch_out (um passo de cada vez, para output_select e seg_display)

Componentes

- MUX

- Registro D

Etapa 10: Saída FSM

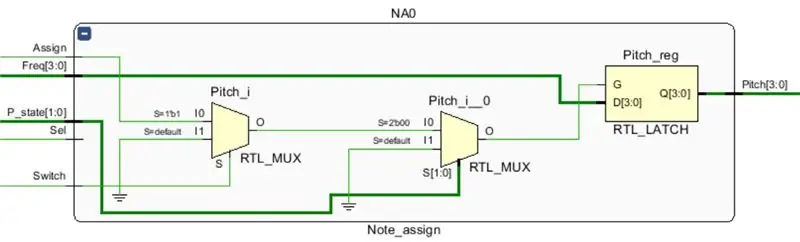

Etapa 11: atribuição de nota

O módulo de atribuição de nota é responsável por atribuir um tom à nota posicional ou passo. Este módulo é bastante simples. Ele primeiro verifica se o circuito está no estado de "seleção" e se uma chave de passo (extrema esquerda) está alta. Se isso for verdade e o botão de atribuição for pressionado, a saída do módulo será igual ao número binário representado pelas chaves de frequência (extrema direita).

Originalmente, tentamos fazer um módulo que salvaria um dos sinais de clock de pitch para a saída, mas tivemos problemas com a mudança de saída para seguir os sinais de clock de entrada. Este é o único módulo usado mais de uma vez no design final. Cada etapa possui um módulo note_assign associado a ela e, por causa disso, cada instância do módulo obtém um bit do barramento Step.

Entradas

- P_state (estado atual de PPS FSM)

- Sel (botão esquerdo)

- Mudar (mudança de uma etapa)

- Freq (interruptores da extrema direita para pitch)

- Atribuir (botão inferior, atribui uma nota)

Saídas

Pitch (número binário, para output_FSM)

Componentes

- MUX

- D resgister

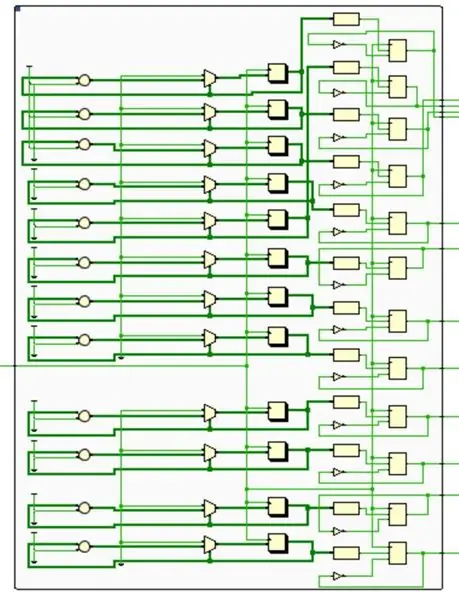

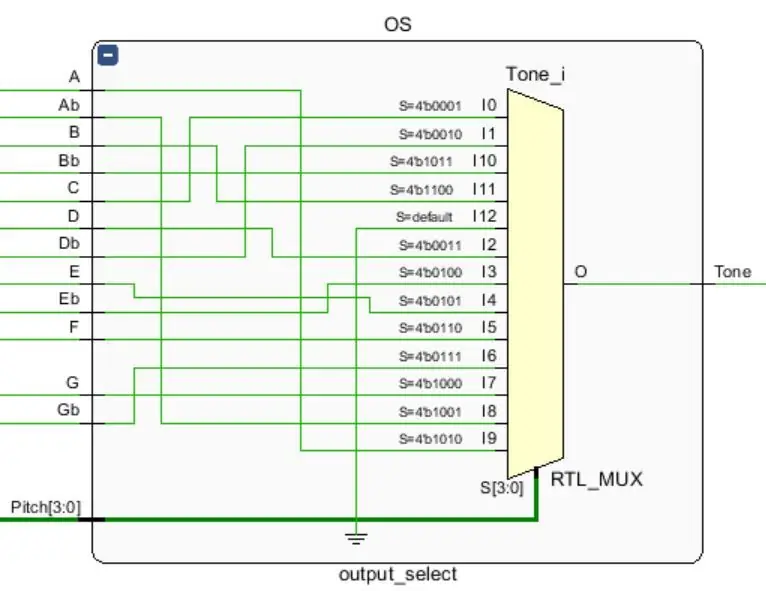

Etapa 12: Seleção de saída

A seleção de saída é responsável por pegar o número binário de uma afinação e conectá-lo ao seu respectivo sinal de clock. Apesar de seu tamanho, este também é um módulo relativamente simples. Output_select é essencialmente um decodificador binário, decodificando o número binário de um pitch para um sinal de clock específico. Na verdade, atribuir a saída a uma frequência de clock funcionou melhor aqui em comparação com o módulo note_assign, porque tudo que esse módulo tinha que fazer era MUX os sinais de clock com o número binário representando a entrada de controle.

Pedimos desculpas pelo estranho roteamento, Vivado organizou os sinais de pitch em ordem alfabética para o arquivo clk_div_pitches, mas para este arquivo ele os organizou por um número binário crescente, fazendo com que os pitches ficassem em uma ordem diferente. Observe também que se o número binário do output_FSM for "0000" ou qualquer coisa maior que "1100", então o MUX enviado através de um sinal '0' simples.

Entrada

- Pitch (de output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (sinais de pitch clock)

Saída

Tom (um único bit que corresponde ao sinal de relógio selecionado, para square_wave)

Componentes

MUX

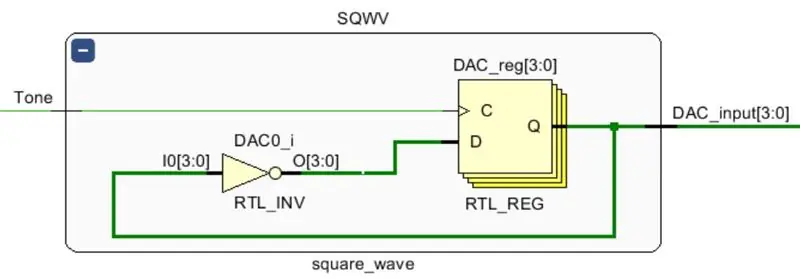

Etapa 13: Square Wave Gen

O módulo square_wave é o gerador da onda quadrada que sai da placa para o DAC. Usando o sinal de tom do arquivo anterior, este square_wave inverte o número de 4 bits entre "0000" e "1111" na borda ascendente do tom. O tom é uma frequência de afinação específica, então square_wave produz uma onda com uma frequência diferente quando output_FSM faz a transição para outro estado. A saída de 4 bits deste módulo vai para o módulo fin_sel, onde a lógica determina se este barramento será enviado com base no estado do PPS FSM.

Uma alternativa a este gerador de onda quadrada é a produção de uma onda senoidal. Embora isso provavelmente produzisse um tom final melhor, é consideravelmente mais difícil de implementar, então optamos por gerar apenas uma onda quadrada.

Entradas

Tom (bit oscilante de output_select)

Saídas

DAC_input (barramento oscilante de 4 bits que muda na mesma frequência de tom)

Componentes

- Inversor

- Registro D

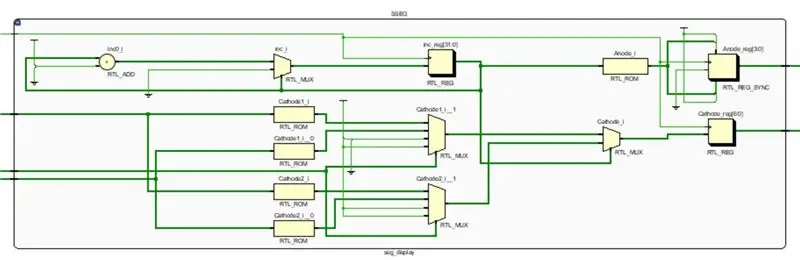

Etapa 14: display de 7 segmentos

O módulo seg_display controla o display de 7 segmentos em nossa placa basys. Dentro do módulo, dois processos ocorrem. O primeiro processo decodifica Freq quando no estado "seleção" ou Pitch quando no modo "play". No modo "pausa", o módulo decodifica para mostrar o símbolo de pausa. Olhando para o código VHDL, você pode ver que o decodificador binário realmente decodifica a entrada em dois sinais diferentes, cátodo1 e cátodo2. Cathode1 representa a letra correspondente ao pitch a ser exibido, e cathode2 representa o símbolo plano (b) se houver. O motivo para isso está relacionado ao segundo processo feito pelo módulo seg_display.

Em uma placa basys3, o display de segmento tem cátodos comuns. Enquanto os anodos controlam qual dígito está ativado, os catodos controlam quais segmentos estão ativados. Como a tela tem cátodos comuns, isso significa que você só pode exibir um conjunto de segmentos por vez. Isso representa um problema para este projeto porque queremos exibir uma letra no primeiro dígito e o símbolo bemol, se necessário, ao mesmo tempo. Agora se lembra do sinal do clock de 7 segundos? Para contornar esse problema, mudamos os ânodos e cátodos para frente e para trás no sinal de clock de 7 segundos. Como o sinal do clock é de 240 Hz e estamos usando dois dígitos, cada dígito oscilará a 60 Hz. Ao olho humano, parecerá que os dígitos não estão oscilando.

Observe também que o display da placa basys3 usa lógica negativa. Isso significa que se um ânodo ou cátodo for definido como '0', esse dígito ou segmento será ativado e vice-versa.

Entradas

- Pitch (número binário para uma nota, usado no estado de reprodução)

- Freq (interruptores de frequência, usados quando no estado de seleção)

- P_state (estado atual de PPS FSM)

- Clk_240Hz (sinal de clock de Clk_div_7seg, duplo 120 porque estamos usando apenas a borda ascendente)

Saídas

- Cátodo (barramento que controla os segmentos na tela, saída final)

- Ânodo (barramento que controla os dígitos no display, saída final)

Componentes

- Robusto

- MUX

- Registro D

Etapa 15: Seleção final

A seleção final é o último módulo usado neste projeto. Outro módulo simples, este módulo controla a saída final que irá para o DAC. Quando estiver no estado de "seleção" ou "pausa", o módulo emitirá um "0000" estático para que nenhuma música seja reproduzida nos alto-falantes. No estado "play", o módulo produzirá os 4 bits oscilantes conforme determinado por square_wave.

Entradas

- P_state (estado atual de PPS FSM)

- DAC_input (os 4 bits oscilantes de square_wave)

Saídas

DAC (igual a DAC_input no estado de jogo, saída final)

Componentes

MUX

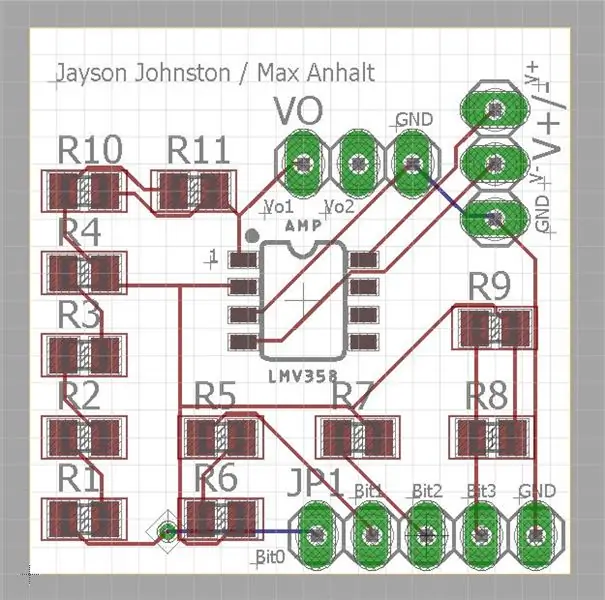

Etapa 16: Dispositivos externos: DAC

Um conversor digital para analógico (DAC) pega um sinal discreto e o converte em um sinal contínuo. Nosso DAC tem quatro bits e é feito de um amplificador somador. Usando uma relação de resistores no circuito de alimentação e feedback, fomos capazes de criar um sistema que produz em 16 níveis diferentes, criando pela "soma" de cada ramificação. Bit0, o ramo superior, carrega o menor peso e contribui com o menor potencial quando alto por causa da maior resistência dos ramos. O peso aumenta conforme você desce pelos galhos. Se você contasse em binário para cima e depois para baixo usando as entradas de bits, as tensões de saída pareceriam uma onda senoidal gradativa. A entrada para o DAC foi conectada a um dos PMODs na placa para transferir o sinal de 4 bits.

O DAC foi originalmente montado para uma aula de Engenharia Elétrica e foi projetado e soldado por nós, não comprado em uma loja. Acima está uma imagem do arquivo de design para a criação da placa de circuito impresso.

Etapa 17: Dispositivos Externos: Alto-falante

Para este projeto, você não vai querer comprar um par de caixas de som super legais. Como você pode ver, o som é bem básico. Nós fomos e compramos um conjunto de alto-falantes de computador por $ 8 na Best Buy. Qualquer coisa com um fone de ouvido funciona bem. Monotone também funciona bem. Você pode até usar fones de ouvido, mas pode estourá-los!

Para conectar a saída do DAC aos alto-falantes, usamos cabos jumper e, em seguida, prendemos o cabo de saída na ponta do conector do fone de ouvido e o cabo de aterramento na base. Tentamos usar fita isolante para segurar os cabos no lugar, mas causou muita interferência. Tentar um estilo diferente de fita pode resolver esse problema.

Para nossos alto-falantes, nós os colocamos na configuração mais alta e obtivemos um ruído decentemente alto.

E essa é a última etapa para criar um sequenciador digital a partir de uma placa FPGA! Vá para as próximas duas seções para baixar todo o nosso código VHDL e ver o sequenciador em ação.

Etapa 18: Demonstração em vídeo

Este vídeo mostra a versão final do projeto de trabalho, incluindo o processo de atribuição dos interruptores a 4 tons distintos e os alto-falantes tocando as respectivas notas.

Etapa 19: Código VHDL

Aqui está o código de todo o projeto, incluindo a restrição e os arquivos sim usados durante a construção do sequenciador. Observe que os arquivos de design não usados dizem isso na arquitetura.

Recomendado:

Sintetizador de sequenciador paralelo: 17 etapas (com imagens)

Parallel Sequencer Synth: Este é um guia para a criação de um sequenciador simples. Um sequenciador é um dispositivo que produz ciclicamente uma série de etapas que acionam um oscilador. Cada etapa pode ser atribuída a um tom diferente e, assim, criar sequências ou efeitos de áudio interessantes

Sequenciador simples: 16 etapas (com imagens)

Sequenciador simples: uma das chaves para fazer boa música é a repetição sem sentido. É nisso que o sequenciador simples é ótimo. Ele faz a mesma coisa repetidamente em uma sequência de oito notas. Você pode ajustar a frequência da nota, a duração da nota e

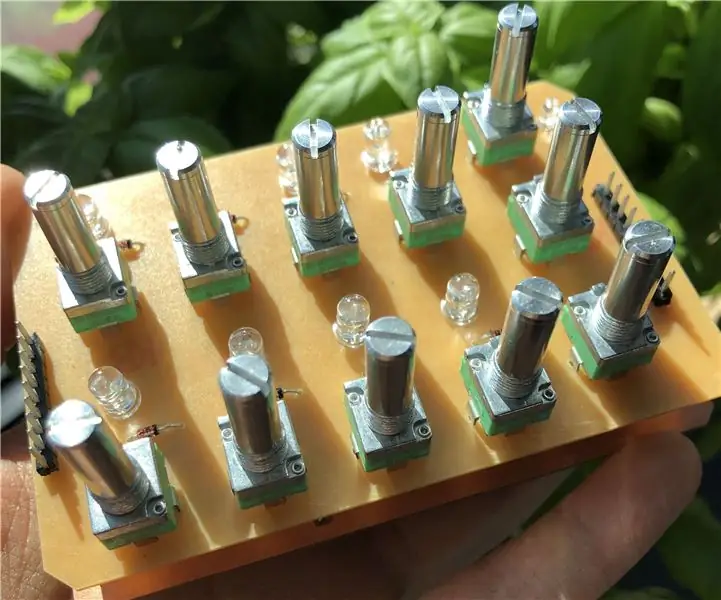

Console Atari Punk com um sequenciador de 8 etapas para bebês: 7 etapas (com fotos)

Console Atari Punk com um sequenciador Baby 8 Step: Esta versão intermediária é o console Atari Punk e o sequenciador Baby 8 Step tudo-em-um que você pode fresar na máquina de fresagem PCB de mesa Bantam Tools Desktop. É composto de duas placas de circuito: uma é uma placa de interface do usuário (IU) e a outra é um utilitário bo

(quase) Programador Universal MIDI SysEx CC (e sequenciador ): 7 etapas (com imagens)

(quase) Programador Universal MIDI SysEx CC (e Sequenciador …): Em meados dos anos oitenta, os fabricantes de sintetizadores iniciaram um programa " menos é melhor " processo que levou a sintetizadores barebones. Isso permitiu a redução de custos do lado do fabricante, mas tornou o processo de patch tediuos, senão impossível para o uso final

Sequenciador de LED RGB programável (usando Arduino e Adafruit Trellis): 7 etapas (com imagens)

Sequenciador de LED RGB programável (usando Arduino e Adafruit Trellis): meus filhos queriam tiras de LED coloridas para iluminar suas mesas, e eu não queria usar um controlador de tira RGB enlatado, porque sabia que eles ficariam entediados com os padrões fixos esses controladores têm. Também achei que seria uma ótima oportunidade para criar