Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:36.

- Última modificação 2025-01-23 15:03.

Nosso objetivo com este projeto era criar algo que economizasse energia e recursos financeiros para as comunidades. Luzes de rua ativadas por movimento fariam ambas as coisas. Em todo o país, a energia está sendo desperdiçada em postes de luz iluminando ruas que estão vazias. Nosso sistema de iluminação pública garante que as luzes sejam acesas apenas quando necessário, economizando dólares incontáveis para as comunidades. Usando sensores de movimento, o sistema liga as luzes apenas quando há carros. Também para a segurança dos pedestres, implantamos um botão de anulação que acende todas as luzes da rua. As etapas a seguir mostrarão como projetamos e construímos nosso modelo reduzido do projeto usando Vivado e uma placa Basys 3.

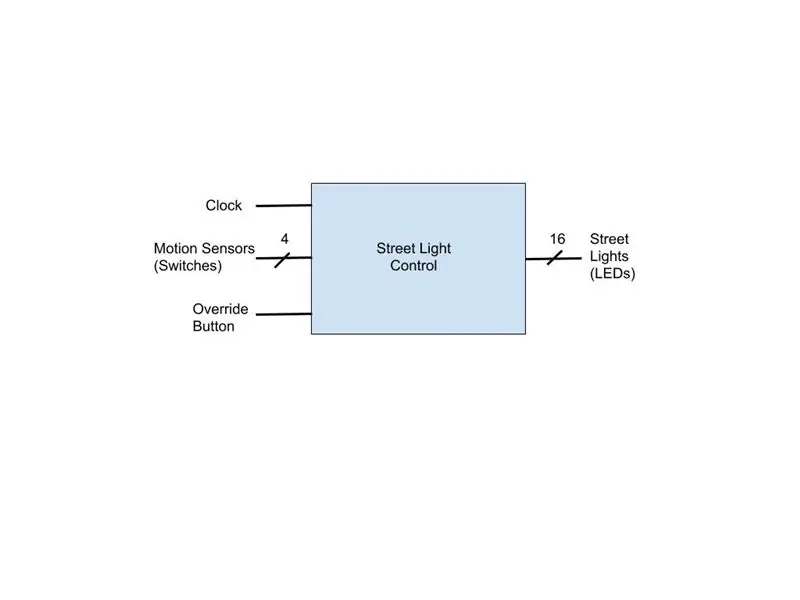

Etapa 1: Caixa Preta do Sistema

Começamos este projeto desenhando um diagrama de caixa preta simples. Um diagrama de caixa preta simplesmente mostra as entradas e saídas que nosso sistema requer para concluir todos os processos necessários. Tentamos manter nosso design o mais simples e básico possível. Nossas três entradas de sistema incluíram um barramento de sensores de movimento (4 para nosso modelo reduzido), um botão de cancelamento de pedestre e uma entrada de relógio. Por outro lado, nossa única saída é um barramento de luzes LED representando nossas luzes de rua. Para este modelo, usamos um cenário de 16 luzes de rua simplesmente porque esse é o número máximo de saídas de LED embutidas na placa Basys 3. Finalmente, usando este diagrama, fomos capazes de criar nosso projeto Vivado, fonte e arquivos de restrição com entradas e saídas apropriadas.

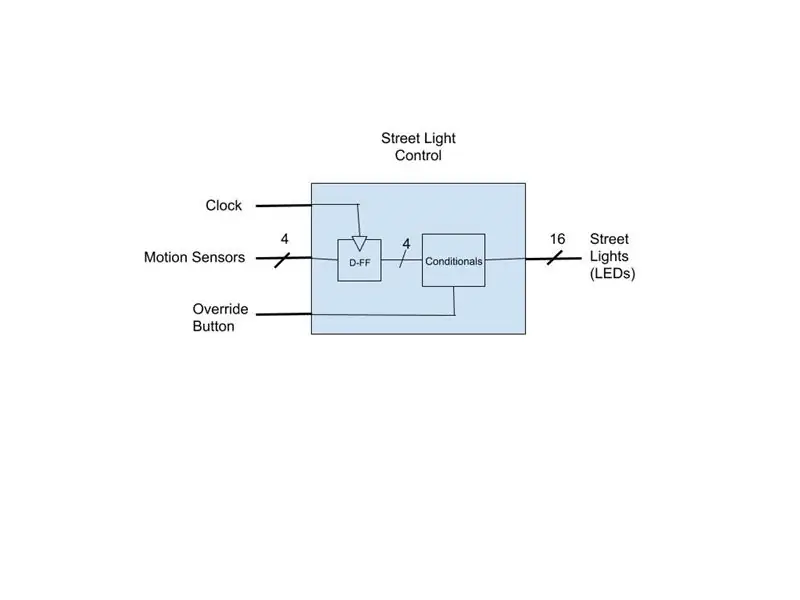

Etapa 2: Componentes

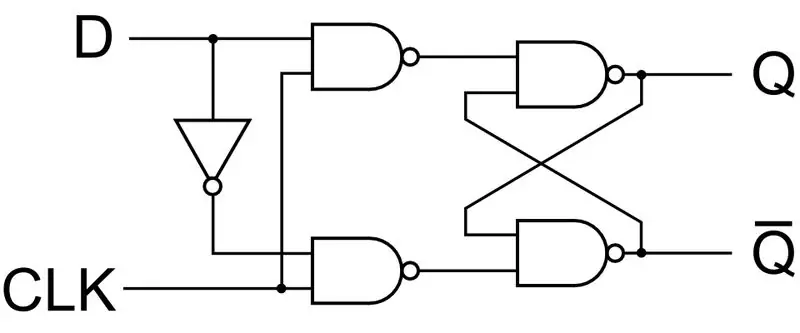

Nesta etapa, vamos nos aprofundar no exame dos componentes que compõem nosso diagrama de caixa preta. Nosso primeiro componente é um arquivo fonte VHDL contendo D flip-flops. Os flip-flops D simplesmente pegam qualquer sinal que esteja sendo recebido dos sensores na borda ascendente do clock e retêm esses dados até a próxima borda ascendente. Isso impede que nossos sensores de movimento sensíveis façam com que os LEDs de saída "pisquem". Além disso, colocamos um único flip-flop D no sinal de entrada do botão para manter os LEDs acesos por cerca de 5 a 7 segundos após o botão ser pressionado. Também executamos isso por meio de um divisor de relógio.

entidade clk_div2 é a porta (clk: in std_logic; sclk: out std_logic); end clk_div2;

arquitetura my_clk_div de clk_div2 é

max_count constante: inteiro: = (300000000); sinal tmp_clk: std_logic: = '0'; começar meu_div: processo (clk, tmp_clk) variável div_cnt: inteiro: = 0; começar if (rise_edge (clk)) then if (div_cnt = MAX_COUNT) then tmp_clk <= not tmp_clk; div_cnt: = 0; senão div_cnt: = div_cnt + 1; fim se; fim se; sclk <= tmp_clk; finalizar processo meu_div; end my_clk_div;

Nosso componente final neste diagrama é um arquivo de origem VHDL comportamental contendo condicionais para as saídas com base na configuração dos sinais de entrada.

Etapa 3: D flip-flops

Os quatro flip-flops anexados aos sinais de entrada são essenciais para a funcionalidade do nosso sistema. Como dito anteriormente, com sensores de movimento sensíveis e um botão de cancelamento, os flip-flops usam travas para apenas emitir nosso sinal de entrada na transição ascendente do clock. Essa lógica sequencial significa que nossas luzes de rua podem permanecer acesas por um determinado período de tempo após serem acionadas por um movimento rápido. A codificação para um D-Flip Flop é bastante simples:

beginprocess (CLK) começa se rise_edge (CLK) then Q <= D; fim se; fim do processo;

A coisa toda pode ser compilada em uma única instrução if. Assim que obtivemos esta peça, criamos um arquivo-fonte VHDL estrutural contendo todos os quatro de nossos flip-flops necessários:

começar DFF0: mapa da porta DFF (CLK => CLK, D => D (0), Q => Q (0)); DFF1: Mapa da porta DFF (CLK => CLK, D => D (1), Q => Q (1)); DFF2: Mapa da porta DFF (CLK => CLK, D => D (2), Q => Q (2)); DFF3: Mapa da porta DFF (CLK => CLK, D => D (3), Q => Q (3));

fim Comportamental;

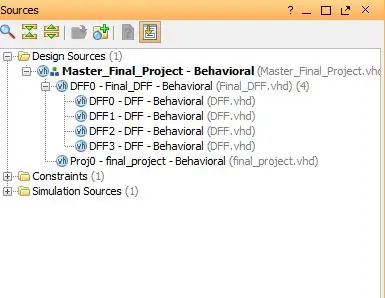

Isso ajuda a manter nosso arquivo estrutural mestre, onde reunimos todos os componentes do sistema muito mais limpos e organizados.

Etapa 4: condicionais

Para manter nosso código compacto e eficiente, escrevemos todas as condicionais em uma única instrução case. Para o nosso modelo reduzido, tínhamos 16 configurações de saída de LED possíveis, pois cada sensor de movimento é responsável por um grupo de 4 LEDs.:

caso NMS é quando "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; caso final;

Etapa 5: restrições

Para indicar adequadamente suas entradas e saídas usando o Vivado, você deve implementar um arquivo de restrição informando todas as portas, botões, LEDs e relógios em uso.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports_property_ LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACKAGE get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property [5] PACKAGE_PIN U14 LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [get 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO PADRÃO LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]} MOSTAR_property [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD 33 get_ports {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD {LVCMOS33 [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports_property_MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_portsIN_property] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Etapa 6: Arquivo-fonte principal

Neste arquivo principal, reunimos todos os arquivos de origem do componente mencionados anteriormente. Este arquivo funciona como código estrutural reunindo os componentes díspares.

entidade Master_Final_Project é a porta (BTN: em STD_LOGIC; CLK: em STD_LOGIC; MS: em STD_LOGIC_VECTOR (3 para 0); LED: para fora STD_LOGIC_VECTOR (15 para 0)); end Master_Final_Project;

arquitetura Comportamental de Master_Final_Project é

componente final_project é a porta (--CLK: em STD_LOGIC; NMS: em STD_LOGIC_VECTOR (3 downto 0); BTN: in STD_LOGIC; --sw: in STD_LOGIC_Vector (1 downto 0); LED: out STD_LOGIC_VECTOR (15 downto 0)); componente final;

componente Final_DFF é

Porta (CLK: em STD_LOGIC; D: em STD_LOGIC_Vector (3 em 0); Q: em STD_LOGIC_Vector (3 em 0)); componente final;

sinal DFF02proj30: STD_LOGIC;

sinal DFF12proj74: STD_LOGIC; sinal DFF22proj118: STD_LOGIC; sinal DFF32proj1512: STD_LOGIC;

começar

DFF0: Mapa da porta Final_DFF (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: mapa da porta final_project (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); fim Comportamental;

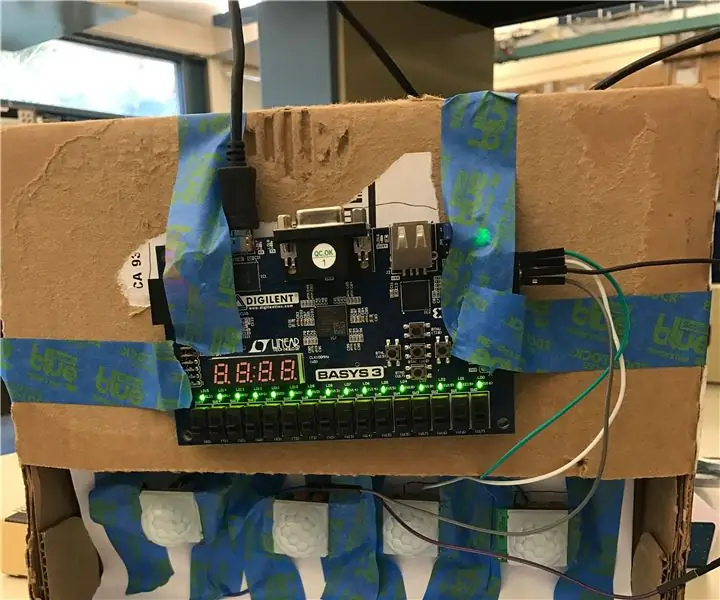

Etapa 7: Montagem

A montagem de hardware para este projeto é mínima. As únicas peças necessárias são as seguintes:

1. Placa Basys 3 (1)

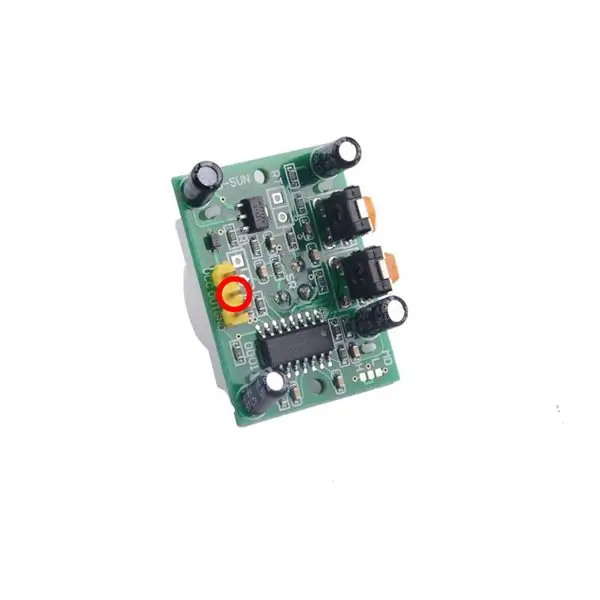

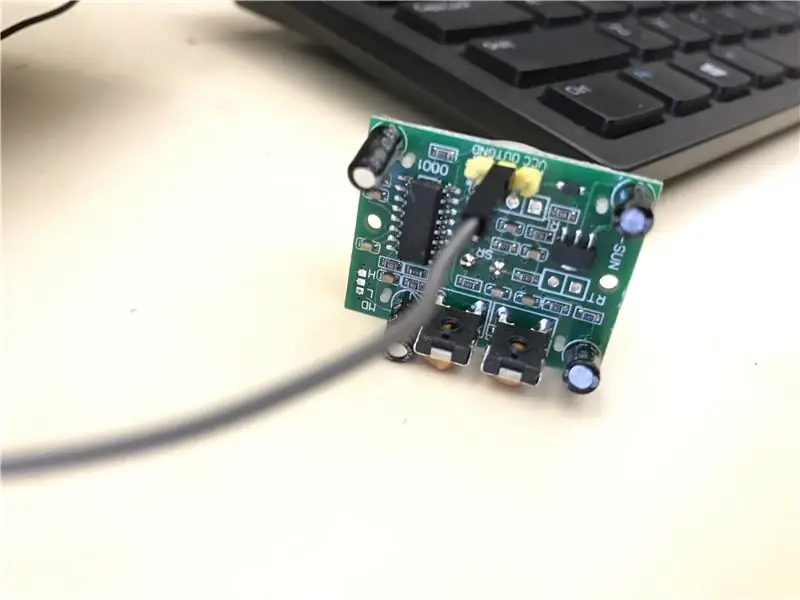

2. Sensores de movimento baratos que podem ser encontrados na Amazon aqui. (4)

3. Eletrodos macho-fêmea (4)

Conjunto:

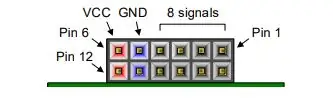

1. Conecte 4 condutores machos às portas 1-4 JB do cabeçalho PMod (consulte a Figura).

2. Conecte as extremidades fêmeas a cada pino de saída do sensor de movimento.

Etapa 8: Carregando o programa

Agora estamos prontos para carregar o arquivo-fonte mestre VHDL na placa Basys 3. Certifique-se de executar a síntese, a implementação e a verificação de fluxo de bits para todos os erros possíveis. Se tudo funcionar com sucesso, abra o gerenciador de hardware e programe o dispositivo Basys 3. Seu projeto agora está concluído!

Recomendado:

Asas de Cosplay ativadas por movimento usando Circuit Playground Express - Parte 1: 7 etapas (com imagens)

Asas de Cosplay ativadas por movimento usando Circuit Playground Express - Parte 1: Esta é a primeira parte de um projeto de duas partes, no qual vou mostrar meu processo para fazer um par de asas de fada automatizadas. A primeira parte do projeto é o mecânica das asas, e a segunda parte é torná-lo usável e adicionar as asas

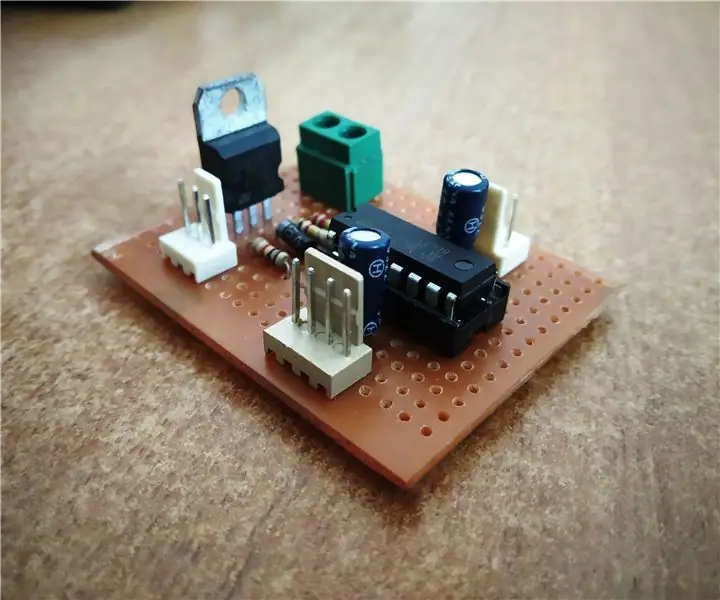

Placa de driver de motor com eficiência energética: 5 etapas

Placa de driver de motor com eficiência energética: O projeto apresentado é uma placa de circuito de motor de passo / driver de motor com IC de driver de motor SN754410 incluindo alguns recursos de economia de energia. A placa pode acionar 2 motores CC ou um motor de passo com a ajuda de um circuito de ponte H duplo no IC. SN754410 IC

Adaptação de luzes LED ativadas por som para uma Jukebox: 4 etapas

Retrofit luzes LED ativadas por som para uma Jukebox: Eu estive pensando em tentar fazer luzes que mudariam de cor no tempo com alguma música, para adicionar a uma jukebox, por um tempo e quando vi o desafio de velocidade da Faixa de LED, e já que estamos trancados no momento, pensei que seria

Sonoff multicanal - Luzes ativadas por voz: 4 etapas (com imagens)

Sonoff multicanal - Luzes ativadas por voz: 5 anos atrás, as luzes da minha cozinha estavam indo bem. A iluminação da pista estava falhando e a iluminação do balcão era apenas lixo. Eu também queria dividir a iluminação em canais para que eu pudesse iluminar melhor a sala para dif

Escadas ativadas por movimento: 6 etapas (com fotos)

Escadas ativadas por movimento: Sim, eu sei o que você está pensando, isso parece um pouco exagero, mas antes de tudo, você nunca terá que se preocupar em dar uma topada no dedão do pé novamente e, em segundo lugar, é muito difícil subir e descer as escadas divertido, eu me peguei subindo as escadas sem motivo