Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:37.

- Última modificação 2025-01-23 15:03.

Neste instrutível, é discutido o projeto de um mestre I2C simples em VHDL.

NOTA: clique em cada imagem para ver a imagem completa

Etapa 1: Visão geral do barramento I2C

• Significa Circuito Integrado Inter.

• Síncrono, Half duplex.

• Interface de dois fios - SDA e SCL.

• SDA - Linha de dados seriais controlada por Mestre e Escravo

• SCL - Relógio Serial gerado pelo Mestre

• Protocolo Multi-master, Multi-slave.

• Dois modos - 100 kbits / seg e 400 kbits / seg: lento e rápido.

Etapa 2: Projeto RTL em VHDL

Especificações de design do nosso mestre I2C

- Quadro de dados de 8 bits.

- Somente controle unidirecional SCL.

- Endereço escravo de 7 bits.

- Suporta modos lento e rápido.

- Único mestre, multi-escravo.

- Em conformidade com as especificações I2C originais da Philips.

O código RTL puro é usado. Portanto, o IP é facilmente transportável em todos os FPGAs. O design compacto baseado em FSM usando relógio gerado internamente garante área e desempenho ideais.

Etapa 3: Simulação e teste

Ambiente de teste

- Simulação funcional e teste usando I2C Slave IP de terceiros.

- Sintetizado usando o conjunto de ferramentas Xilinx Vivado.

- Implementado e testado na placa Artix-7 FPGA.

- Projeto de temporização verificada para 100 MHz.

- Formas de onda testadas em DSO / CRO.

- Comunicação testada com sucesso com Arduino UNO como I2C Slave.

Etapa 4: notas importantes

- Ao testar o mestre usando I2C Slave IP, configure o código do escravo de acordo com seus requisitos. Você pode querer alterar a frequência do relógio padrão e o endereço do escravo. A frequência do relógio também deve ser configurada no código mestre.

- Durante o teste on-board, não se esqueça dos resistores pull-up, pois a linha SDA é uma saída de dreno comum !!! Verifique no google o resistor pull-up recomendado para diferentes velocidades i2c. Usei 2,2K para 100 kHz.

- Se não estiver usando a bancada de teste e simular o Master de forma independente, simule cuidadosamente o sinal SDA, pois é um sinal bidirecional (inout). Possui dois drivers, lado mestre e lado escravo. Você deve saber quando 'forçar' e quando 'desforçar'.

- SCL é uma linha unidirecional. Não há necessidade de puxar para cima.

- Por favor, vá até a Documentação IP completamente.

Etapa 5: arquivos anexados

- Todos os códigos RTL do I2C Master.

- Bancada de teste, códigos I2C Slave também, para teste.

- Documentação IP.

Para qualquer dúvida, sinta-se à vontade para entrar em contato comigo:

Mitu Raj

siga-me:

Para dúvidas, entre em contato: iammituraj@gmail.com

Recomendado:

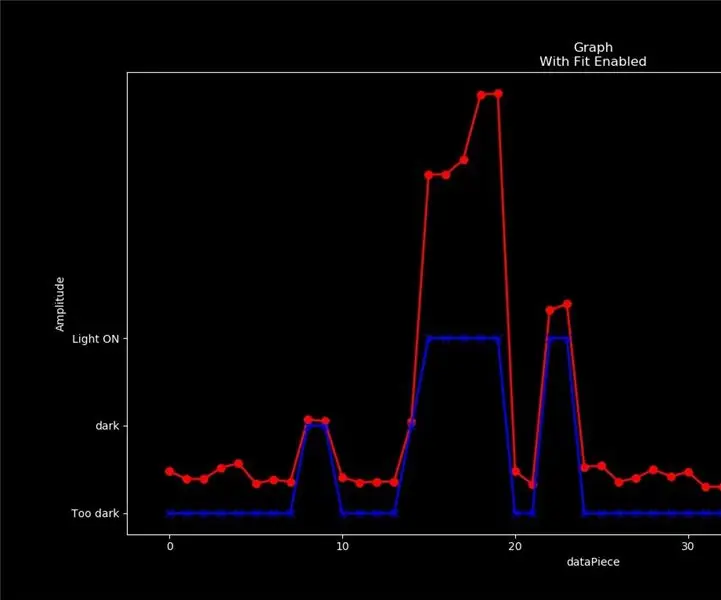

Plotagem de intensidade de luz usando Arduino e a biblioteca mestre de Arduino do Python: 5 etapas

Plotagem de intensidade de luz usando Arduino e a biblioteca mestre de Arduino do Python: Arduino sendo uma ferramenta econômica, mas altamente eficiente e funcional, programá-lo em Embedded C torna o processo de criação de projetos tedioso! O módulo Arduino_Master do Python simplifica isso e nos permite realizar cálculos, remover valores de lixo

Gardenduino Aka, o Mestre do Jardim: 4 Passos

Gardenduino Aka, o Mestre do Jardim: bem, não é entediante limpar nossos gramados, regar as plantas & o que não! Bem, exatamente jardinagem não é minha xícara de chá. então resolvi fazer um sistema automático para cuidar do meu jardim! vamos começar

Projeto do Mestre SPI em VHDL: 6 etapas

Projeto de SPI Master em VHDL: Neste instrutível, vamos projetar um SPI Bus Master do zero em VHDL

Torre do Portal 2 - Controle da Torre Mestre: 9 etapas (com imagens)

Portal 2 Turret - Master Turret Control: Este projeto é uma extensão ou remix do meu Portal Turret original em Instructables (Portal-2-Turret-Gun). Ele também pode ser usado como um controlador barato para controlar qualquer coisa que use o chip de rádio nRF24L01. A tela LCD é particularmente útil quando

Relógio mestre baseado em Arduino para escolas: 9 etapas (com imagens)

Relógio mestre para escolas baseado em Arduino: se sua escola, escola de crianças ou outro local depende de um relógio mestre central que está quebrado, você pode ter um uso para este dispositivo. Novos relógios principais estão disponíveis, é claro, mas os orçamentos das escolas estão sob pressões extremas, e é realmente um sati