Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:37.

- Última modificação 2025-01-23 15:03.

Neste instrutível, vamos projetar um SPI Bus Master do zero em VHDL.

Etapa 1: Visão geral do SPI

- SPI é um barramento serial síncrono

- Sua popularidade e simplicidade o tornaram um padrão de fato na comunicação serial

- Barramento full-duplex

- Protocolo simples e entre os barramentos seriais mais rápidos

Etapa 2: especificações de design

Estas são as especificações do SPI Master que iremos projetar:

- Suporta todos os quatro modos de operação; configurável dinamicamente

- Controle de ativação do relógio para economia de energia

- Comprimento da palavra configurável estaticamente e velocidade

- Interrupção única para transmissão e recepção

Etapa 3: começando

Em primeiro lugar, nosso IP deve ter duas interfaces. Uma é a interface serial e a outra é a interface paralela. A interface serial consiste nos sinais padrão de fato de SPI: MOSI, MISO, SS, SCLK.

MOSI às vezes é chamado de SDO e MISO às vezes é chamado de SDI.

A interface serial é usada para se comunicar com periféricos externos, ou seja, escravos SPI.

A interface paralela é usada para se comunicar com nosso host, isto é, um microcontrolador ou microprocessador, que realmente informa ao Mestre quais dados devem ser transmitidos e recebidos em série através das linhas seriais. ou seja, todos os barramentos de dados pertencem à interface paralela.

Temos um relógio global que comanda a lógica SPI interna, bem como SCLK, que geramos internamente.

Também temos alguns sinais de controle, como ativação de gravação e ativação do relógio. E interrupções e outros sinais de status.

Visto que temos que lidar com condições de controle complexas, é mais simples projetar IPs de comunicação serial como um FSM. Também projetaremos o mestre SPI como um FSM. O FSM será acionado por outro relógio interno que é duas vezes SCLK. Esse relógio interno é gerado usando contadores síncronos do relógio global.

Todos os sinais de controle que cruzam os domínios do clock têm sincronizadores para estar no lado mais seguro.

Etapa 4: Visualização RTL do núcleo mestre SPI e formas de onda de simulação

É um projeto RTL simples, sem o uso de IPs FPGA dedicados. Portanto, é um código totalmente portátil para qualquer FPGA.

Recomendado:

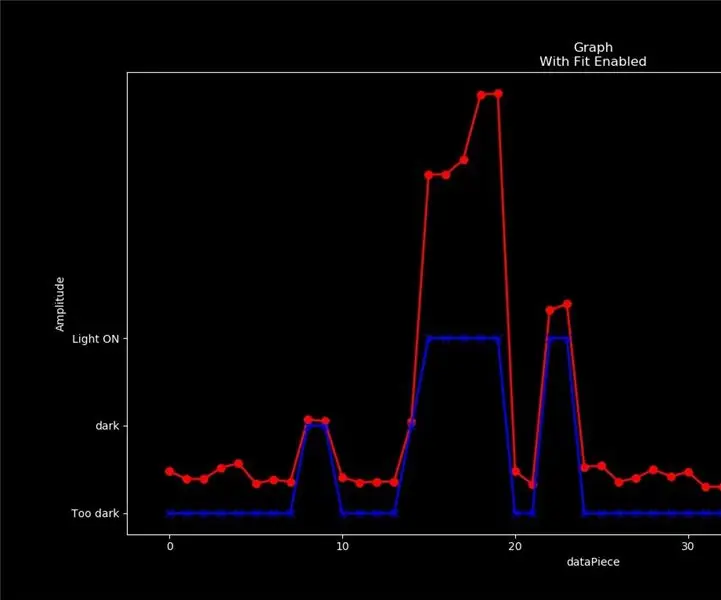

Plotagem de intensidade de luz usando Arduino e a biblioteca mestre de Arduino do Python: 5 etapas

Plotagem de intensidade de luz usando Arduino e a biblioteca mestre de Arduino do Python: Arduino sendo uma ferramenta econômica, mas altamente eficiente e funcional, programá-lo em Embedded C torna o processo de criação de projetos tedioso! O módulo Arduino_Master do Python simplifica isso e nos permite realizar cálculos, remover valores de lixo

Gardenduino Aka, o Mestre do Jardim: 4 Passos

Gardenduino Aka, o Mestre do Jardim: bem, não é entediante limpar nossos gramados, regar as plantas & o que não! Bem, exatamente jardinagem não é minha xícara de chá. então resolvi fazer um sistema automático para cuidar do meu jardim! vamos começar

Projeto do Mestre I2C em VHDL: 5 etapas

Projeto do mestre I2C em VHDL: Neste instrutível, é discutido o projeto de um mestre I2C simples em VHDL. NOTA: clique em cada imagem para ver a imagem completa

Torre do Portal 2 - Controle da Torre Mestre: 9 etapas (com imagens)

Portal 2 Turret - Master Turret Control: Este projeto é uma extensão ou remix do meu Portal Turret original em Instructables (Portal-2-Turret-Gun). Ele também pode ser usado como um controlador barato para controlar qualquer coisa que use o chip de rádio nRF24L01. A tela LCD é particularmente útil quando

Relógio mestre baseado em Arduino para escolas: 9 etapas (com imagens)

Relógio mestre para escolas baseado em Arduino: se sua escola, escola de crianças ou outro local depende de um relógio mestre central que está quebrado, você pode ter um uso para este dispositivo. Novos relógios principais estão disponíveis, é claro, mas os orçamentos das escolas estão sob pressões extremas, e é realmente um sati