Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:37.

- Última modificação 2025-01-23 15:03.

Neste instrutível, vamos projetar um controlador VGA simples em RTL. O controlador VGA é o circuito digital projetado para controlar monitores VGA. Ele lê o Frame Buffer (memória VGA) que representa o quadro a ser exibido e gera os dados necessários e os sinais de sincronização para fins de exibição.

Se você estiver procurando por código Verilog / System verilog: Visite meu blog VGA Controller and Video System in Verilog

Etapa 1: Interface de um controlador VGA

A seguir estão os principais sinais de interface em um controlador VGA

- Relógio Pixel ou Relógio VGA

- Sinais HSYNC e VSYNC

Para o monitor VGA escolhido, você deve primeiro calcular a frequência do Pixel Clock necessária para acioná-lo. Depende de 3 parâmetros: Pixels horizontais totais, Pixels verticais totais, Taxa de atualização da tela.

Normalmente, F = THP * TVP * Taxa de atualização

Encontre a documentação sobre o clock de pixel necessária para vários monitores VGA, no RAR anexo.

Os sinais HSYNC e VSYNC são gerados a partir do clock de Pixel. O tempo dos sinais HSYNC e VSYNC depende do número de parâmetros: Pórtico frontal horizontal e vertical, Pórtico traseiro horizontal e vertical, Pixels de exibição horizontal e vertical, Larguras e polaridades de pulso de sincronização vertical e horizontal.

Esses parâmetros são padronizados para um monitor VGA escolhido. Encontre esses documentos no RAR anexo.

Esses parâmetros são parâmetros configuráveis em nosso IP do controlador VGA.

Etapa 2: Integrar o controlador VGA a um monitor VGA

A figura mostra como integrar o controlador VGA a um monitor VGA. Você precisa de mais dois componentes para completar o sistema:

- Buffer de quadro: Memória que contém o quadro a ser exibido.

- Vídeo DAC: DAC que converte dados digitais RGB e aciona o monitor VGA com sinais analógicos RGB no nível de tensão apropriado.

Um dos Video DACs mais simples e populares é o ADV7125. É um DAC de 8 bits que converte palavras digitais RGB em sinais analógicos de 0-0,7 V e direciona a exibição VGA.

Etapa 3: Design de buffer de quadro

É a memória que 'armazena' a imagem a ser exibida. Normalmente é uma RAM ou, às vezes, ROM. Discutiremos como projetar um frame buffer para representar uma imagem. O buffer de quadros passa essas informações digitais para um comando Video DAC on do controlador VGA.

Primeiro, temos que decidir a profundidade de pixels necessária. Ele decide a qualidade da imagem, a variedade de cores que um pixel pode representar. Para um DAC de 8 bits, precisamos representar os componentes da cor primária de um pixel: R, G e B em 8 bits cada. Isso significa que um pixel é de 24 bits.

Cada pixel é armazenado de maneira contígua nos locais da memória Frame Buffer.

Suponha que uma imagem a ser exibida tenha 800 x 600 pixels.

Portanto, o Frame Buffer necessário é 800x600 = 480000 x 24 bits de memória

O tamanho total da memória é 800x600x24 = 1400 kB aprox.

Se for uma imagem em preto e branco, 800x600x1 = 60 kB aprox.

Block RAMs podem ser usados para representar um Frame Buffer em FPGAs Xilinx.

Etapa 4: Notas

- Sinais adicionais são necessários no controlador VGA dependendo do DAC escolhido. Eu usei ADV7125.

- Adicione atrasos de ciclo por meio de flip-flops em VSYNC e HSYNC antes de acionar a exibição VGA. Isso ocorre por causa das latências do DAC e da memória. Os sinais de pixel devem ser sincronizados com HSYNC e VSYNC. No meu caso, foi um atraso de 2 ciclos.

- Se o Frame Buffer de determinado tamanho não puder ser projetado no FPGA devido à limitação do tamanho da memória do bloco, use uma memória menor para representar a imagem e simplesmente edite o código para rolar o endereço no limite da memória disponível, ao invés do limite do quadro completo. Isso irá replicar a mesma imagem indefinidamente em toda a tela. Outro método é o escalonamento de pixels, no qual cada pixel é replicado para mostrar a imagem inteira em tela cheia, em uma resolução menor. Isso pode ser feito ajustando a lógica de incremento de endereço no código.

- O IP é totalmente portátil em todos os FPGAs e sua temporização é verificada em até 100 MHz no Virtex-4 FPGA.

Etapa 5: arquivos anexados

O RAR contém:

- Código do controlador VGA

- PDFs de padrões VGA.

Recomendado:

Sensor de alarme de porta de interruptor magnético, normalmente aberto, projeto simples, 100% funcionando, código-fonte fornecido: 3 etapas

Sensor de alarme de porta de chave magnética, normalmente aberto, projeto simples, 100% funcionando, código-fonte fornecido: Descrição: Oi pessoal, vou fazer um tutorial sobre o alarme de sensor de chave magnética MC-18 que opera no modo normalmente aberto. Tipo de interruptor: NÃO (tipo normal fechado), o circuito está normalmente aberto e o circuito é conectado quando o ímã está próximo. A palheta

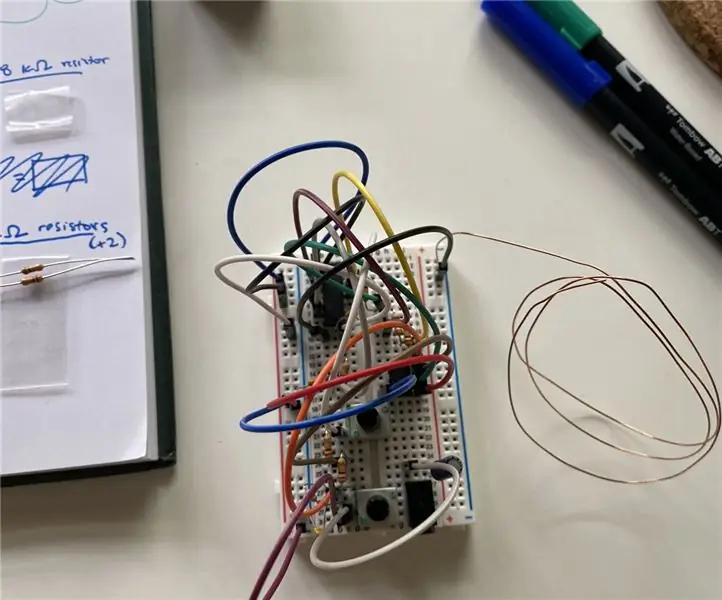

Projeto final PHYS 339: Theremin Simples: 3 etapas

PHYS 339 Projeto Final: Simple Theremin: Como músico recreativo e físico, sempre achei que theremins são os instrumentos eletrônicos mais legais. Seu som é quase hipnótico quando tocado por um profissional, e a teoria da eletrônica necessária para que funcionem é bastante s

Projeto de um controlador de cache associativo conjunto de quatro vias simples em VHDL: 4 etapas

Projeto de um controlador de cache associativo de conjunto de quatro vias simples em VHDL: No meu instrutivo anterior, vimos como projetar um controlador de cache mapeado direto simples. Desta vez, damos um passo à frente. Estaremos projetando um controlador de cache associativo de conjunto de quatro vias simples. Vantagem? Menos taxa de erros, mas ao custo de desempenho

Projeto de um controlador de interrupção programável em VHDL: 4 etapas

Projeto de um controlador de interrupção programável em VHDL: Estou impressionado com o tipo de respostas que recebo neste blog. Obrigado pessoal por visitar meu blog e me motivar a compartilhar meu conhecimento com vocês. Desta vez, vou apresentar o design de outro módulo interessante que vemos em todos os SOCs - Interromper C

Projeto de um controlador de cache simples em VHDL: 4 etapas

Projeto de um controlador de cache simples em VHDL: Estou escrevendo este instrutível, porque achei um pouco difícil obter algum código VHDL de referência para aprender e começar a projetar um controlador de cache. Portanto, desenvolvi um controlador de cache do zero e testei-o com sucesso em FPGA. Eu tenho p