Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:35.

- Última modificação 2025-01-23 15:03.

JDM é um programador PIC popular porque usa uma porta serial, um mínimo de componentes e não requer fonte de alimentação. Mas há confusão por aí, com muitas variações de programador na rede, quais funcionam com quais PICs? Neste “instrutível” colocamos o JDM à prova e eu demonstro como simular o circuito usando o Spice que vai responder a todas as suas perguntas!

Suprimentos

LTspice, que pode ser baixado de Analog Devices aqui.

Você também precisa dos arquivos de circuito JDM aqui.

Etapa 1: Requisitos da porta serial

O JDM requer uma porta serial que atenda às especificações EIA232, idealmente com níveis de tensão de + 12 / -12.

De acordo com a folha de dados do driver de linha MC1488 da Texas Instruments (Figura 3)

Impedância de saída = 4V / 8mA = 500 ohm.

Limite de corrente de curto-circuito = 12mV, sem limite de tempo - nenhum dano ao chip.

Impedância de entrada do receptor de linha = 3k a 7k ohm recomendado.

As portas seriais em PCs desktop mais antigos usam + 12 V / -12 V atendendo a esse requisito.

As portas seriais em notebooks mais novos usam tensões mais baixas. JDM pode ou não funcionar - a resposta é mais complexa.

Etapa 2: Requisitos de programação PIC

As informações sobre os requisitos de programação do PIC são obtidas na Microchip. A descrição acima é para um dispositivo típico.

Etapa 3: Especificação JDM

O site original do JDM se perdeu nas brumas do tempo? Isso nos deixa adivinhando o que o designer originalmente pretendia para a especificação.

- Fornece VDD = 5V e até IDD = 2mA máximo (para a versão “no soquete”)

- Fornece VHH = 13V e até IHH = 0,2mA no máximo.

- MCLR Rise time tVHHR = 1uS máx.

- A versão ICSP deve ser capaz de puxar MCLR baixo contra aumento de 22k no alvo.

Etapa 4: Descrição do circuito

A Figura JDM1 é baseada no circuito JDM “padrão” obtido do site PICPgm. Este é o programador “PIC in Socket” onde o PIC obtém energia dos pinos TX e RTS. O diagrama original era difícil de entender, então eu o redesenhei usando a convenção normal de fluxo de corrente de cima para baixo. E eu adicionei indicadores LED “RESET”, “PROG” e “RTS” que são necessários durante a construção e os testes. Esperançosamente, isso não terá nenhum efeito prejudicial sobre o comportamento.

A convenção normal do projeto do circuito é o comum de todos os aterramentos, mas o recurso principal do JDM é que o aterramento da porta serial (GND) é conectado ao VDD. Isso cria confusão, pois os sinais da porta serial são medidos em relação aos sinais GND e PIC em relação ao aterramento lógico (VSS).

Quando TX fica alto, Q1 se comporta como dois diodos polarizados para frente. (O coletor Q1 não tem polarização reversa como na operação normal do transistor). O coletor Q1 carrega C2, que é fixado em VDD + 8V por Zener (D3). O emissor Q1 fornece 13 V ao MCLR para o modo de programa / verificação.

Quando TX fica baixo, o capacitor C3 é carregado por meio de D1 e VSS é fixado em VDD-5V por zener (D5). Também TX é fixado em (VSS-0,6) por D1. Q1 está desligado, C1 mantém sua carga para o próximo pulso de programação. O MCLR é fixado em 0 V por D2, então o PIC agora é reiniciado.

Quando o RTS é alto, o relógio é transmitido para o PGC. D4 clamp PGC na lógica VDD alta. Quando o RTS é baixo, o capacitor C3 é carregado por meio de D6 e o VSS é fixado em VDD-5V por zener (D5). D6 fixa PGC em VSS ou lógica 0.

Durante a programação, os dados enviados no DTR são lidos no PGD, que o PIC configura como entrada. Quando o DTR está alto, Q2 atua como “seguidor de emissor” e a tensão PGD é de aproximadamente (VDD-0,6) ou lógica 1. Quando o DTR está baixo, Q2 atua como um transistor ruim (pinos do emissor e do coletor invertidos). Q2 puxa PGD para baixo, que é fixado por D7 no VSS ou lógico 0.

Durante a verificação, o PIC configura o PGD como uma saída para enviar dados para a porta serial. O DTR deve ser definido como alto e os dados são lidos no CTS. Quando a saída PGD é alta, Q2 está desligado, CTS = DTR = + 12V. Quando a saída PGD está baixa, Q2 está ativado. O coletor Q2 consome corrente (12V + 5V) / (1k + 1k5) = 7mA do DTR e puxa o CTS para baixo, para o VSS.

Etapa 5: Prepare-se para a simulação

Baixe o LT Spice, salve e abra os arquivos de circuito (*.asc) fornecidos aqui. Para simular o circuito, devemos fornecer a ele algumas entradas e, em seguida, “rastrear” as saídas. V1, V2 V3 simula a porta serial de 12 V com impedância de saída R11, R12, R13.

- V1 gera 2 pulsos de programa em TX de 0,5 ms a 4,5 ms

- V2 gera rajadas de pulsos de dados no DTR de 1,5 a 4,5 ms

- V3 gera rajadas de pulsos de clock no RTS de 0,5 a 3,5 ms

Os componentes V4, X1, R15 e R16 fazem parte da simulação.

- V4 gera 2 pulsos de 2,5 a 4,5 ms para verificar os dados.

- O jumper X1 simula OUTPUT no PGD.

- R15, R16 simulam o “carregamento” do PIC no VDD e MCLR.

Etapa 6: Modificações para ICSP

A Figura JDM3 mostra a versão para programação “no circuito”. As modificações do original são

- Substitua o soquete ZIF pelo conector ICSP.

- O PIC agora é alimentado pelo fornecimento ao circuito de destino (V5).

- Remova o zener 5V (D5).

- O pequeno capacitor 100pF (C4) é movido próximo ao PIC no circuito alvo.

- Os LEDs obtêm energia da placa de circuito sempre que possível.

- O resistor pull-up MCLR (R10) e o diodo (D10) são necessários no circuito de destino.

- AVISO. O alvo deve ter uma fonte “flutuante”, de preferência uma bateria.

- Não conecte o aterramento alvo (VSS) ao aterramento do computador / PC conectando qualquer outra porta do computador ao mesmo tempo que o JDM.

Depois de simular JDM1, o problema do longo tempo de carga em C2 tornou-se aparente. Então, depois de ler Fruttenboel, parece que C2 e Q1 foram adicionados como uma modificação ao original. Não consigo imaginar o que C2 e Q1 pretendem fazer além de criar problemas. Portanto, para o JDM4, voltamos ao design antigo do Fruttenboel, que é simples e fácil de entender. D1 e D3 / LED2 fixam MCLR entre VSS e VDD + 8V. O valor de R1 é reduzido para 3k3, apenas o suficiente para iluminar o LED2 em 12V.

O JDM4 também foi projetado para funcionar com portas seriais mais fracas. Quando TX fica alto (+ 9V), fonte de corrente TX = (9-8) / (1k + 3k3) = 0,2ma, apenas o suficiente para puxar MCLR alto, embora insuficiente para iluminar o LED2. Quando TX fica baixo (cerca de -7V), dissipador de corrente TX = (9-7) / 1k = 2mA. Corrente LED1 = (7-2 para led) / (2k7) = 1.8mA. MCLR pull down current = 7-5.5 / 3k3 = 0.5mA.

Este circuito também foi testado (simulação JDM5) para ver o que acontece com portas seriais +/- 7V mínimo, onde há tensão insuficiente para sustentar VHH = 13V. O propósito de C1 agora se torna aparente, C1 cria um impulso + ve curto para MCLR, um pico de 33us na borda ascendente de TX, suficientemente longo para o PIC entrar no modo de programação, talvez? Mas remova o jumper X2 (desative o LED1), pois não há corrente suficiente para reduzir o MCLR e iluminar o LED1 juntos. Quando TX fica baixo, afundamento de corrente TX = (7V-5.5V) / (1k + 3k3) = 0,3mA, apenas o suficiente para puxar MCLR baixo contra o pull-up R10.

Etapa 7: Resultados da simulação

Para visualizar os arquivos gráficos, é melhor clicar com o botão direito nos links abaixo e selecionar "Abrir link em uma nova guia"

Simulação 1: rastreamento de MCLR, VSS e RTS para JDM1 original. Imediatamente as observações 1, 2 e 3 são aparentes.

Simulação 2: rastreamento de MCLR e VSS, e RTS para JDM2 modificado, que corrige problemas anteriores.

Simulação 3: rastreamento de PGD, VSS e PGC para JDM2 enviando dados em modo de programa. Observação 4 a 3,5mS.

Simulação 4: rastreamento de PGD, VSS e CTS para JDM2 em modo de verificação (jumper X1 inserido). OK

Simulação 5: traço de MCLR, VSS, PGD e PGC para JDM3. ICSP usando energia do circuito resolve muitos problemas.

Simulação 6: rastreamento de MCLR, VSS, PGD e PGC para JDM4 com porta serial +/- 9V. MCLR sobe imediatamente, funcionando totalmente.

Simulação 7: rastreamento de MCLR, VSS e TX para JDM5 com porta serial +/- 7V e jumper X2 removido. C1 cria um aumento de + ve (pico) na borda ascendente do MCLR, quase o suficiente para empurrar o MCLR acima de TX para 13V.

Etapa 8: Conclusões

O Spice é realmente bom em revelar “segredos ocultos” da operação do circuito. Evidentemente o circuito JDM funciona e é compatível com muitos chips PIC, mas as observações a seguir revelam possíveis limitações / problemas de compatibilidade / falhas?

- Tempo de subida longo de MCLR enquanto C2 carrega para VPP no primeiro pulso de TX. Falha na especificação 3.

- A porta serial cobra C2 quando TX fica alto e RTS fica baixo. Mas o RTS também tem a função de carregar o C3. Quando ambos ocorrem ao mesmo tempo, isso cria mais carga no RTS, conseqüentemente C3 perde carga (VSS sobe) em 2 ms na simulação. Falha na especificação 1.

- C3 perde carga (VSS começa a subir) depois que os pulsos de clock param em 3,5 ms.

- Qual é o propósito de C2, ele é necessário?

Soluções

- Presumivelmente, o PICPgm usa uma “rodada de trabalho” de software. Ele deve aplicar um pulso TX longo para pré-carregar em C2 e, em seguida, entrar no modo de programação somente após o segundo pulso TX? Para a simulação, reduzi o valor de C2 para 1uF para dar um tempo de subida de 1 ms. Não é uma solução ideal.

- Divida C2 e C3 para que sejam carregados independentemente. Uma pequena modificação em JDM2, C2 é referenciado a GND em vez de VSS.

- Resolvido por JDM3. O ICSP é muito mais confiável porque o PIC é alimentado pelo circuito de destino.

- O JDM4 resolve o problema 1. Este é um projeto simples, eliminando C2 por completo.

Etapa 9: e finalmente

A prova do pudim está no comer. Este JDM funciona, então continue usando.

E minhas recomendações são:

- usar JDM2 para programação de soquete e portas seriais de 12V,

- use JDM4 para programador ICSP e portas seriais acima de +/- 9V,

- use JDM4 com jumper X2 removido para portas seriais acima de +/- 7V.

Referências:

Especiaria Analog Devices LT

picpgm

Fruttenboel

Siga mais projetos PIC em sly-corner

Recomendado:

Revisão do kit Elegoo Super Started Uno R3: 4 etapas

Elegoo Super Started Kit Uno R3 Review: Alguns dias atrás Elegoo me enviou este Super Starter Kit para teste. Então, vamos ver o que há dentro. Ao abrir esta caixa compacta, podemos ver muitas coisas. Na capa há um índice com todos os componentes. Dentro, temos um cartão de agradecimento com todos os s

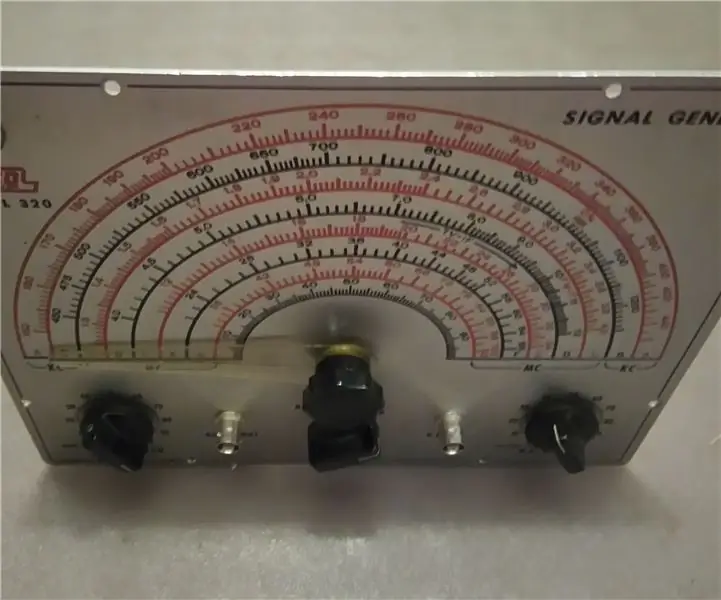

Revisão completa do gerador de sinal vintage: 8 etapas

Revisão Completa do Gerador de Sinal Vintage: Adquiri um gerador de sinal Eico 320 RF em uma feira de troca de rádio amador por alguns dólares há alguns anos, mas nunca tive tempo de fazer nada com ele até agora. Este gerador de sinal tem cinco faixas selecionáveis de 150 kHz a 36 MHz e com ha

Revisão de Bionicle Nuparu Matoran: 4 etapas

Revamp Bionicle Nuparu Matoran: Esta é essencialmente a minha reformulação de um dos meus matoran bionicle favoritos, Nuparu. Basicamente, ele tem pernas, tronco e braços personalizados, além de um robótico. Embora seja pequeno, este modelo é um pouco difícil para os construtores pela primeira vez. Mesmo se você não

Reparação e revisão do obturador Olympus Pen-EE: 16 etapas

Reparação e revisão geral do obturador Olympus Pen-EE: A Olympus Pen-EE, de cerca de 1961, pode ser desmontada com cuidado, limpa e revisada e remontada sem muito risco de perder qualquer peça ou danificar qualquer coisa dentro - se você estiver disponível , firme e paciente, e você tem a ferramenta certa

Guia de revisão do Acer Extensa Laptop 5620 Hotrod: 12 etapas

Acer Extensa Laptop 5620 Guia de revisão do Hotrod: Nosso pequeno Acer Extensa 5620 tem sido bom para nós nos últimos dois anos, hein? É uma máquina boa o suficiente … mas … você está sentindo isso também, certo? Rodando um pouco lento, disco rígido fazendo barulho, a bateria dura menos de vinte minutos … está na hora