Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:35.

- Última modificação 2025-01-23 15:03.

Como gerar baixo ruído, alta precisão e gerador de RF estável (com modulação AM, FM) no Arduino.

Suprimentos

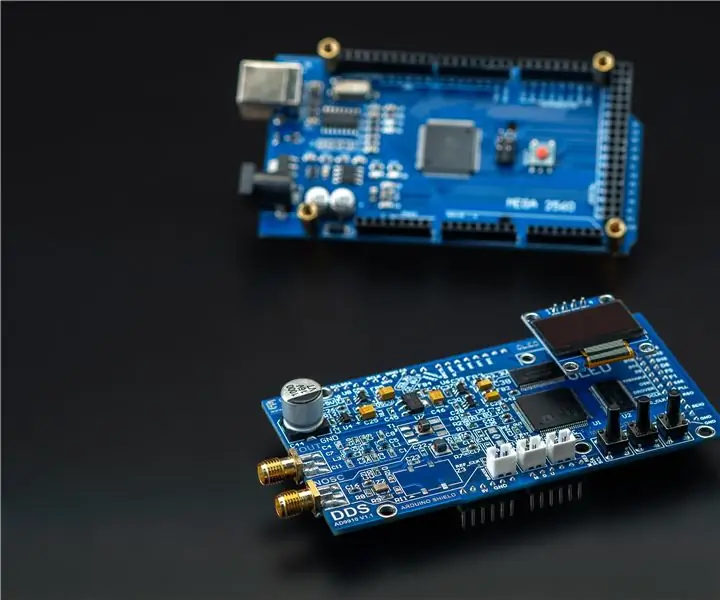

1. Arduino Mega 2560

2. Exibe OLED de 0,96"

3. DDS AD9910 Arduino Shield

Etapa 1: Instalação de Hardware

Juntar as peças

1. Arduino Mega 2560

2. Exibe OLED de 0,96"

3. DDS AD9910 Arduino Shield

gra-afch.com/catalog/arduino/dds-ad9910-arduino-shield/

Etapa 2: Instalando o software

Pegamos o firmware daqui e compilamos no IDE do arduino

github.com/afch/DDS-AD9910-Arduino-Shield/…

Etapa 3: Ajuste

Um gerador de 40 MHz foi usado em nossa placa, então fazemos essas configurações

Etapa 4: Obtemos o resultado muito melhor do que a bordo da China

Conseguimos o resultado muito melhor do que a bordo da China!

Havia muitos harmônicos e espúrios na tela na placa de chine, e seu nível chegou a -25 dBm! E isso apesar do fato de que de acordo com a documentação da Analog Devices para AD9910 o nível de harmônicos não deve ultrapassar -60 dBm. Mas nesta placa há harmônicos em torno de -60 dBm! Este é um bom resultado!

Ruído de Fase

Este parâmetro é muito importante e interessante para quem compra DDS. Uma vez que o ruído de fase intrínseco do DDS é obviamente menor do que o dos geradores PLL, o valor final é altamente dependente da fonte do clock. Para atingir os valores declarados na folha de dados em AD9910, ao projetar nosso DDS AD9910 Arduino Shield, seguimos estritamente todas as recomendações de dispositivos analógicos: layout de PCB em 4 camadas, fonte de alimentação separada de todas as 4 linhas de energia (3,3 V digital, 3,3 V analógico, 1,8 V digital e 1,8 V analógico). Portanto, ao comprar nosso DDS AD9910 Arduino Shield, você pode se concentrar nos dados do datasheet do AD9910.

A Figura 16 mostra o nível de ruído ao usar o PLL integrado no DDS. O PLL multiplica a frequência de um gerador de 50 MHz por 20 vezes. Usamos uma frequência semelhante - 40 MHz (Multiplicador x25) ou 50 MHz (Multiplicador x20) da TCXO, o que dá ainda mais estabilidade.

E a figura 15 mostra o nível de ruído ao usar um clock externo de referência de 1 GHZ, com o PLL desligado.

Comparando esses dois gráficos, por exemplo, para Fout = 201,1 MHz e o PLL interno ativado no deslocamento da portadora de 10 kHz, o nível de ruído de fase é -130 dBc @ 10 kHz. E com o PLL desligado e usando clock externo, o ruído de fase é 145 dBc @ 10kHz. Ou seja, ao usar um ruído de fase de clock externo em 15 dBc melhor (menor).

Para a mesma frequência Fout = 201,1 MHz, e o PLL interno ativado em 1 MHz de deslocamento da portadora, o nível de ruído de fase é -124 dBc @ 1 MHz. E com o PLL desligado e usando clock externo, o ruído de fase é de 158 dBc @ 1 MHz. Ou seja, ao usar um ruído de fase de clock externo em 34 dBc melhor (menor).

Conclusão: ao usar clocking externo, você pode obter ruído de fase muito mais baixo do que usar o PLL embutido. Mas não se esqueça de que, para alcançar tais resultados, requisitos maiores são apresentados ao gerador externo.

Etapa 5: Plotagens

Plotagens com ruído de fase

Recomendado:

Como usar o gerador de sinal de frequência Arduino DDS AD9850: 7 etapas

Como usar o Arduino DDS Frequency Signal Generator AD9850: Neste tutorial, aprenderemos como fazer um gerador de sinais de frequência usando um módulo AD9850 e Arduino. Assistir ao vídeo! Nota: Consegui obter a frequência de até + 50 MHz, mas a qualidade do sinal fica pior com as frequências mais altas

Vocal GOBO - Escudo de Amortecimento de Som - Cabine Vocal - Caixa Vocal - Filtro de Reflexão - Escudo de Voz: 11 Passos

Vocal GOBO - Sound Dampener Shield - Vocal Booth - Vocal Box - Reflexion Filter - Vocalshield: Comecei a gravar mais vocais no meu home studio e queria obter um som melhor e depois de algumas pesquisas descobri o que é um " GOBO " era. Eu tinha visto essas coisas abafadoras de som, mas realmente não sabia o que elas faziam. Agora eu faço. Eu encontrei um y

Construir este gerador de sinal de varredura LED de 5 Hz a 400 KHz a partir de kits: 8 etapas

Construa este gerador de sinal de varredura de LED de 5 Hz a 400 KHz a partir de kits: Construa este gerador de sinal de varredura fácil a partir de kits prontamente disponíveis. na época, que era um gerador de sinais. Eu queria um

Gerador de sinal / função DIY DDS barato: 4 etapas (com imagens)

Gerador de Sinal / Função DDS DIY Barato: Essas placas de módulo Gerador de Sinal DDS podem ser adquiridas por apenas $ 15 se você olhar ao redor. Eles irão gerar formas de onda seno, quadradas, triangulares, dente de serra (e reversas) (e algumas outras) com bastante precisão. Eles também têm controles de toque, amplitude

Gerador de função DIY (ICL8038) 0 Hz - 400 kHz: 11 etapas

Gerador de Função DIY (ICL8038) 0 Hz - 400Khz: Os Geradores de Função são uma ferramenta muito útil em bancada de eletrônicos, mas pode ser bastante caro, mas temos muitas opções para construí-lo de maneira econômica. Neste projeto, usamos ICl8038