Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:35.

- Última modificação 2025-01-23 15:03.

Por AmCoderhttps://www.linkedin.com/in/mituFollow Mais do autor:

Sobre: Mitu Raj - Just a Hobbyst and Learner - Chip Designer - Software Developer - Física e Matemática Entusiasta Mais sobre AmCoder »

## Este é o link mais clicado e popular no Google para implementação de VHDL do ALGORITMO CORDIC para gerar ondas seno e cosseno ## Atualmente, existem muitos algoritmos eficientes de hardware, mas estes não são bem conhecidos devido ao domínio dos sistemas de software sobre muitos anos. CORDIC é um algoritmo que nada mais é do que um conjunto de lógicas de deslocamento e adição usadas para calcular uma ampla gama de funções, incluindo certas funções trigonométricas, hiperbólicas, lineares e logarítmicas. Este é o algoritmo usado em calculadoras, etc. Assim, usando apenas shifters e somadores simples, podemos projetar um hardware com menos complexidade, mas com potência de DSP, usando um algoritmo cordic. Portanto, ele pode ser projetado como um projeto RTL simples em VHDL ou Verilog sem usar unidades de ponto flutuante dedicadas ou IPs matemáticos complexos.

Etapa 1: VHDL e Modelosim

Aqui, o algoritmo cordic é implementado usando VHDL para gerar uma onda senoidal e uma onda cose. Pode produzir seno e cosseno do ângulo de entrada com grande precisão. O código é sintetizável em FPGA. O Modelsim é usado para simular o projeto e a bancada de testes.

Etapa 2: Código VHDL para o Design e o Banco de Teste

A técnica de escalonamento binário é usada para representar números de ponto flutuante.

Por favor, vá até os documentos em anexo antes de codificar.

Go thruSimulating cordic_v4.vhd - O Design -A entrada é um ângulo em 32 bits + bit de sinal; pode processar qualquer ângulo de 0 a +/- 360 graus com precisão de entrada de 0,000000000233 graus. Ao fornecer a entrada -> MSB é o bit de sinal e os 32 bits restantes representam a magnitude. - A saída do projeto é seu valor de seno e cos em 16 bits + bit de sinal. com precisão 0,00001526. Observe que a saída é exibida na forma de complemento de 2 se o respectivo valor de seno ou cos for negativo. Simulando testb.vhd - Test Bench For The Design (1) Ângulos de entrada e redefinir pull = '0'. Após duas etapas da simulação, puxe o reset para '1' e "execute tudo". (2) Na janela de simulação, defina a raiz dos sinais sen e cos como decimal e formato> Analógico (automático). (3) Afaste o zoom para ver a forma de onda devidamente.

Etapa 3: arquivos anexados

(1) cordic_v4.vhd - Design. (2) testb.vhd - Bancada de teste para o design.

(3) Documento sobre como forçar entradas de ângulos e converter os resultados binários.

Atualização: ESTES ARQUIVOS SÃO OBSELETOS E NÃO FORNECIDOS MAIS. USE OS ARQUIVOS DA PRÓXIMA ETAPA

Etapa 4: Mini-Cordic IP Core - 16 bits

A limitação da implementação acima é - frequência de operação lenta e inferior do clock devido à realização de cálculos em um único ciclo de clock. Mini-Cordic IP Core - 16 bits

- Caminhos críticos distribuídos em vários ciclos para melhorar o desempenho.- Mais rápido - Design comprovado em FPGA sintetizado em clock de 100 Mhz.- Mais área otimizada em HDL, hardware menor.- Sinais de status de carga e conclusão adicionados.- Apenas a desvantagem é a resolução menor em comparação com o anterior. Bancada de teste:

completamente automatizado de entradas de ângulo de 0 a 360 graus

Arquivos anexados: 1) mini cordic main vhdl file2) mini cordic test bench3) Mini Cordic IP Core manual4) Doc sobre como forçar ângulos e converter resultados

Para qualquer dúvida, sinta-se à vontade para entrar em contato comigo:

Mitu Raj

siga-me:

mail: iammituraj@gmail.com

### Total de downloads: 325 até 01-05-2021 ###

### Código editado pela última vez: julho-07-2020 ###

Recomendado:

Robô de auto-equilíbrio - Algoritmo de controle PID: 3 etapas

Robô de Auto Balanceamento - Algoritmo de Controle PID: Este projeto foi concebido porque eu estava interessado em aprender mais sobre Algoritmos de Controle e como implementar efetivamente loops PID funcionais. O projeto ainda está em fase de desenvolvimento, pois um módulo Bluetooth ainda não foi adicionado, o que

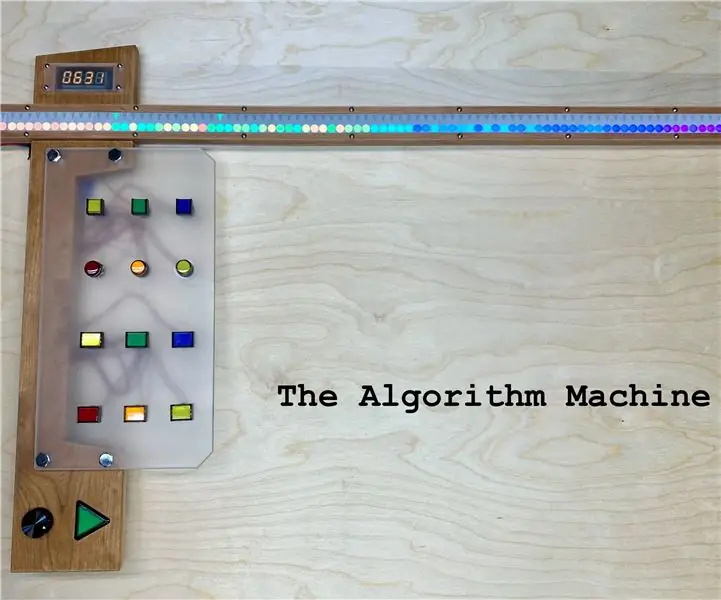

A máquina de algoritmo: 13 etapas (com imagens)

A máquina de algoritmo: ensino ciência da computação em nível universitário há 15 anos e, embora minha especialidade seja mais no lado de programação, ainda passo muito tempo cobrindo algoritmos padrão para pesquisa e classificação. Do ponto de vista do ensino que

Robô de autoequilíbrio usando algoritmo PID (STM MC): 9 etapas

Robô de Auto Balanceamento Usando Algoritmo PID (STM MC): Recentemente, muito trabalho foi feito no auto balanceamento de objetos. O conceito de auto-equilíbrio começou com o equilíbrio do pêndulo invertido. Esse conceito se estendeu também ao design de aeronaves. Neste projeto, criamos um pequeno mod

Jogo da velha no Arduino com IA (algoritmo Minimax): 3 etapas

Jogo da velha no Arduino com IA (algoritmo Minimax): Neste Instructable, irei mostrar a você como construir um jogo da velha com uma IA usando um Arduino. Você pode jogar contra o Arduino ou assistir o Arduino jogar contra si mesmo. Estou usando um algoritmo chamado " algoritmo minimax "

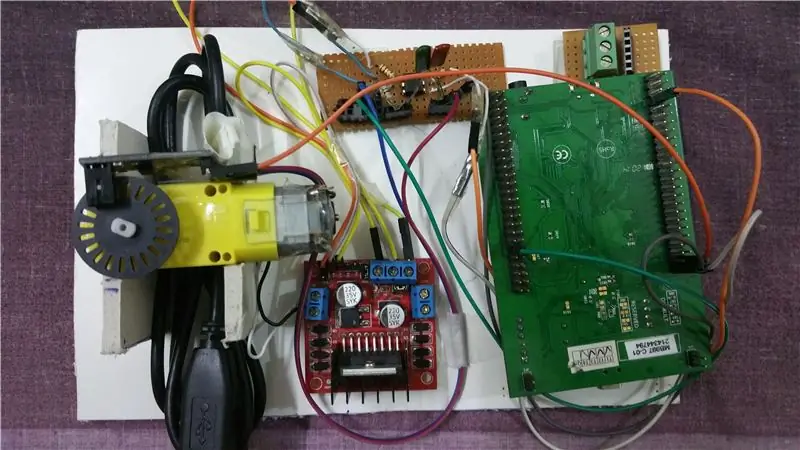

Controle de velocidade do motor DC usando o algoritmo PID (STM32F4): 8 etapas (com imagens)

Controle de velocidade do motor DC usando o algoritmo PID (STM32F4): Olá a todos, Este é tahir ul haq com outro projeto. Desta vez, é STM32F407 como MC. Este é um projeto de fim de semestre. Espero que gostem. Requer muitos conceitos e teoria, por isso vamos examiná-los primeiro. Com o advento dos computadores e