Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:39.

- Última modificação 2025-01-23 15:03.

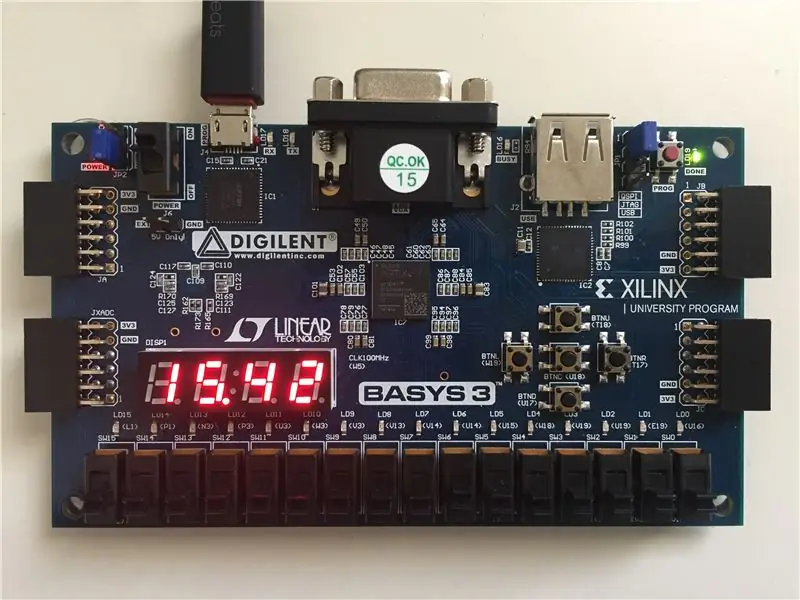

Este é um tutorial sobre como fazer um cronômetro usando VHDL e uma placa de circuito FPGA, como uma placa Basys3 Atrix-7. O cronômetro pode contar de 00,00 segundos a 99,99 segundos. Ele usa dois botões, um para o botão start / stop e outro para o botão reset. Os números são exibidos no display de sete segmentos da placa usando seus ânodos e cátodos. Existem três arquivos diferentes necessários para que este cronômetro funcione.

Etapa 1: Hardware / Software

- Placa FPGA Basys3 Atrix-7

- Suíte Vivado Design de Xilinx

- USB 2.0 A Macho para Micro-B Macho

Etapa 2: Diagrama de blocos

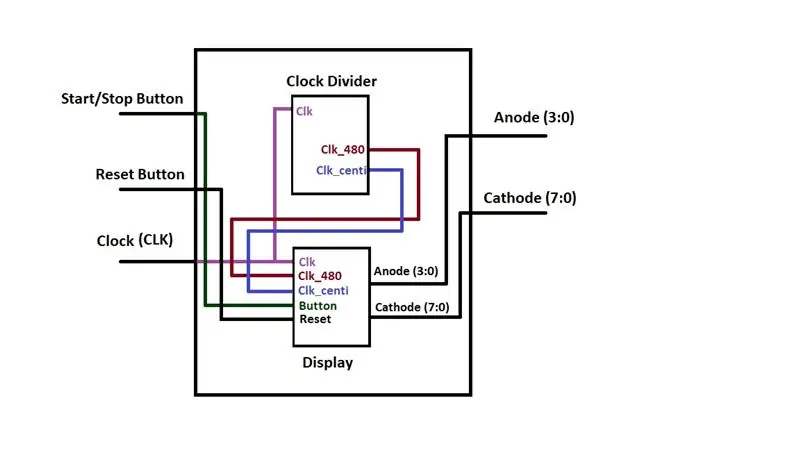

O cronômetro geral tem três entradas e duas saídas. As três entradas são start / stop, reset e clock. O start / stop e o reset são botões e o clock é o clock de 100MHz da placa. As duas saídas são os ânodos e cátodos para o display de sete segmentos.

O primeiro módulo (divisor de clock) tem uma entrada e duas saídas. A entrada é o clock de 100 MHz da placa e as saídas são dois relógios separados, um funcionando a 480 Hz e outro funcionando a 0,5 MHz.

O segundo módulo (display) possui cinco entradas e duas saídas. As entradas são o relógio de 100 MHz da placa, os dois relógios do módulo divisor de relógio e os botões iniciar / parar e reiniciar. As saídas são os ânodos e cátodos.

O último módulo (modelado por todo o diagrama de blocos) possui três entradas e duas saídas. Este é o arquivo que reúne tudo. As entradas são os 100MHz da placa e os botões start / stop e reset. As saídas são os ânodos e cátodos que controlam o display de sete segmentos. Todas as entradas e saídas estão fisicamente na placa para o módulo final.

Etapa 3: Diagrama de estado

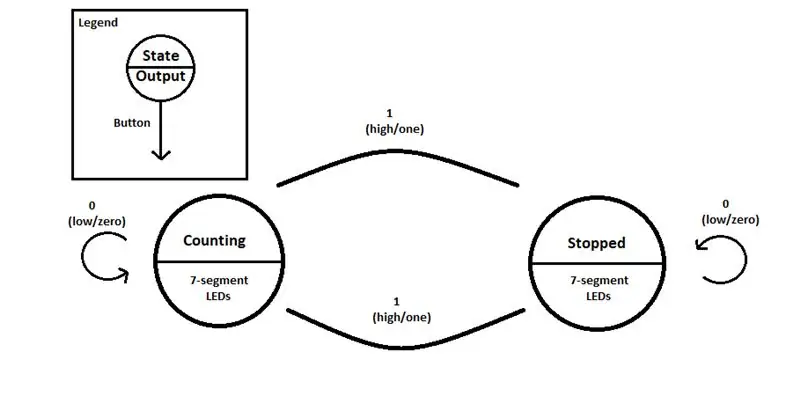

A imagem acima mostra o diagrama de estado de como o cronômetro funciona. Pressionar o botão de reinicialização não afeta o estado do cronômetro. O próximo estado é determinado pelo botão start / stop. O start / stop é "HIGH" quando pressionado, mas não quando é mantido pressionado, e "LOW" quando o botão é recuperado ou mantido pressionado após ser "HIGH" momentaneamente.

Se o cronômetro estiver contando e o botão Iniciar / Parar ficar "ALTO", ele interromperá a contagem. Se o cronômetro for parado e o botão Iniciar / Parar ficar "ALTO", ele começará a contar novamente. Para ambos os estados, se o botão Iniciar / Parar estiver "BAIXO", ele permanecerá no estado em que está atualmente.

Etapa 4: Módulo Divisor de Relógio

O módulo divisor de clock tem uma entrada, o clock de 100 MHz da placa, e duas saídas, os relógios de 480 Hz e 0,5 MHz. O clock de 480 Hz é usado para manter todos os LEDs no display de sete segmentos "ligados" ao mesmo tempo, alternando entre os quatro rapidamente. O relógio de 0,5 MHz é usado para que o cronômetro realmente conte por centi-segundos.

Etapa 5: Módulo de exibição

Este módulo de exibição tem cinco entradas, o relógio de 100 MHz da placa, os dois relógios do módulo de relógio e os botões liga / desliga e reset, e duas saídas, os anodos e catodos. Este módulo também possui a "lógica" de como o cronômetro conta e incorpora a máquina de estados finitos.

Etapa 6: Módulo de ligação

Este módulo final é aquele que reúne os outros dois módulos. Ele tem três entradas, o relógio de 100 MHz da placa e os botões start / stop e reset, e duas saídas, os ânodos e os cátodos. O relógio de 100 MHz vai para o módulo divisor de relógio e o módulo de display, e os botões start / stop e reset vão para o módulo de display. As saídas do módulo divisor de clock (480Hz e 0,5 MHz) vão para as duas entradas de clock do módulo de display. As saídas do módulo de display (ânodos e cátodos) vão para as saídas do módulo final.

Etapa 7: restrições

As duas entradas podem ser quaisquer botões na placa FPGA Basys3 Atrix-7 e as saídas serão os quatro ânodos e os oito cátodos (porque você também quer um ponto decimal entre segundos e milissegundos) para o display de sete segmentos.

Etapa 8: Pronto

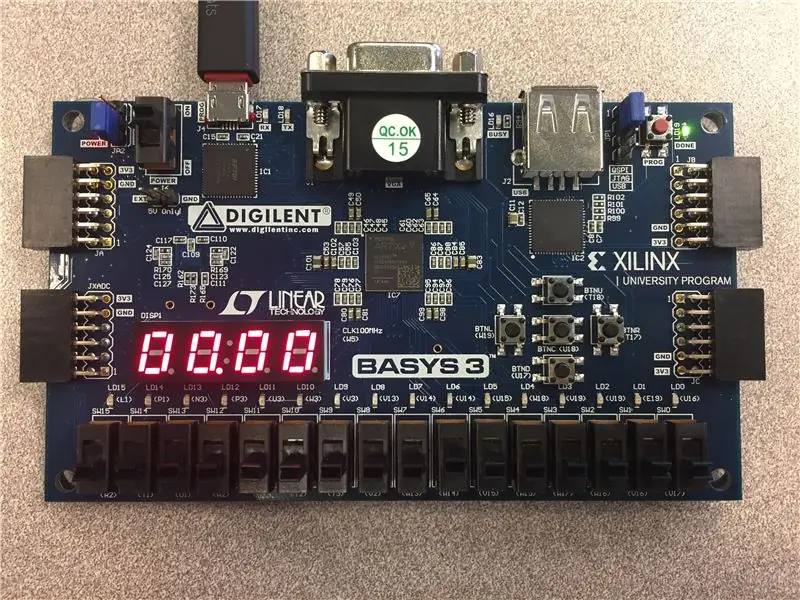

Carregue o programa em sua placa FPGA Basys3 Atrix-7 e pressione o botão start / stop para fazer o cronômetro funcionar!

Recomendado:

Relógio WiFi, cronômetro e estação meteorológica, Blynk controlado: 5 etapas (com imagens)

Relógio WiFi, temporizador e estação meteorológica, Blynk controlado: Este é um relógio digital Morphing (graças a Hari Wiguna pelo conceito e código de metamorfose), é também um relógio analógico, estação meteorológica e cronômetro de cozinha. É totalmente controlado por um Aplicativo Blynk em seu smartphone por WiFi. O aplicativo permite que você

Cronômetro de Croakers: 16 etapas (com imagens)

Cronômetro de Croakers: Se você sorrir para os sapos, alguns deles vibrarão. Compreendendo o movimento, pode-se saber o tempo - uma operação instável. Frogs " olhando para cima " representam as horas em binário (da esquerda para a direita; 8,4,2,1) .Frogs " olhando para a frente " representa min

Cronômetro digital tudo em um (relógio, cronômetro, alarme, temperatura): 10 etapas (com imagens)

Cronômetro Digital All in One (Relógio, Cronômetro, Alarme, Temperatura): Estávamos planejando fazer um Cronômetro para alguma outra competição, mas posteriormente também implementamos um relógio (sem RTC). À medida que entramos na programação, nos interessamos em aplicar mais funcionalidades ao dispositivo e acabamos adicionando DS3231 RTC, como

Cronômetro básico usando VHDL e Basys3 Board: 9 etapas

Cronômetro básico usando VHDL e placa Basys3: Bem-vindo ao instrutivo sobre como construir um cronômetro usando VHDL básico e placa Basys 3. Estamos ansiosos para compartilhar nosso projeto com você! Este foi um projeto final para o curso CPE 133 (Design Digital) na Cal Poly, SLO no outono de 2016. O projeto que construímos

Cronômetro VHDL de um minuto: 5 etapas

Cronômetro de um minuto VHDL: Este é um tutorial sobre como construir um cronômetro de um minuto usando VHDL e uma placa Basys 3. Esse dispositivo é ideal para jogos em que cada jogador tem no máximo um minuto para fazer sua jogada. O cronômetro exibe com precisão os segundos e milissegundos o