Índice:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:36.

- Última modificação 2025-01-23 15:03.

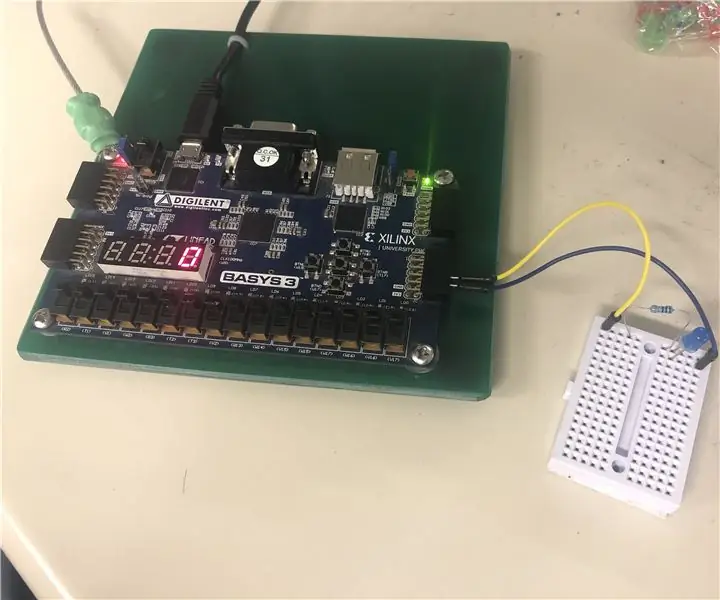

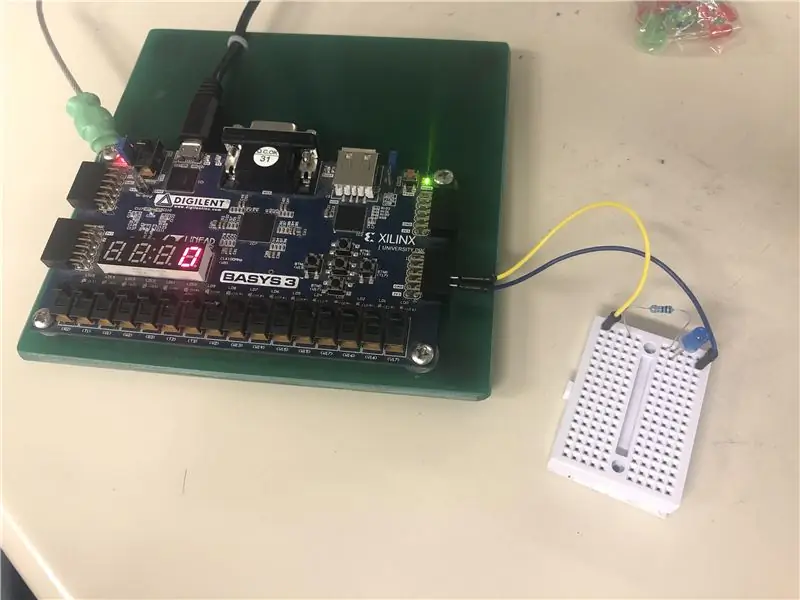

Neste guia, vamos construir e controlar um sistema externo de dimerização de LED. Com os botões disponíveis, o usuário pode reduzir a luminosidade da lâmpada LED para qualquer brilho desejado. O sistema usa a placa Basys 3 e é conectado a uma placa de ensaio que contém um resistor e a lâmpada LED. Pressionar o botão "para cima" designado aumentará o brilho e pressionar o botão "para baixo" diminuirá o brilho até zero. Isso não apenas evita que o usuário seja cegado por lâmpadas brilhantes como o sol, mas também conserva energia!

Etapa 1: Criar contador de entrada

Para esta etapa, criamos o componente que determina o nível de brilho (através de um relógio) usando dois interruptores: um para aumentar e outro para diminuir. Usando VHDL, produzimos o contador com o uso de D flip-flops. Pressionar o botão "para cima" empurra o próximo estado para o estado atual, emitindo para o display de sete segmentos e a lâmpada LED.

entidade updown_counter é

Porta (estado_atual: out STD_LOGIC_VECTOR (3 downto 0); estado_ anterior: in STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; down_enable: in STD_LOGIC; up_enable: in STD_LOGIC); end updown_counter; arquitetura O comportamento de updown_counter é iniciar flop: processo (next_state, clk, up_enable, down_enable, previous_state) begin if (altitude_de_conta (clk)) then if (up_enable = '1' e não (next_state = "0000")) then present_state <= next_state; elsif (down_enable = '1' e não (previous_state = "1111")) then present_state <= previous_state; fim se; fim se; fracasso do processo final; fim Comportamental;

Também precisamos de um relógio para cada entrada a ser travada (quando aumenta), por isso também criamos um divisor de relógio que determina a rapidez com que os botões podem ser pressionados entre cada nível de brilho. Este divisor de relógio nos permite exibir corretamente o nível certo no display de sete segmentos e produzir o nível certo de intensidade para cada nível.

entidade counter_clkDiv é

Porta (clk: em std_logic; sclk: fora de std_logic); end counter_clkDiv; arquitetura my_clk_div de counter_clkDiv é constante max_count: inteiro: = (10000000); sinal tmp_clk: std_logic: = '0'; começar meu_div: processo (clk, tmp_clk) variável div_cnt: inteiro: = 0; comece if (rise_edge (clk)) then if (div_cnt> = MAX_COUNT) then tmp_clk <= not tmp_clk; div_cnt: = 0; senão div_cnt: = div_cnt + 1; fim se; fim se; sclk <= tmp_clk; finalizar processo meu_div; end my_clk_div;

Etapa 2: Criar Divisor de Relógio LED

Para esta etapa, criamos um divisor de relógio para a lâmpada LED para determinar 16 níveis diferentes de intensidade. Com 0 desativado para 15 exibindo o brilho máximo, o divisor de relógio incrementa cada pressionamento de botão de acordo com o que definimos como os níveis de brilho. Cada nível crescente significava um aumento no relógio da lâmpada LED. Lembrando que o brilho não aumenta linearmente, nós giramos o relógio para o máximo que poderia ir e diminuímos nossos relógios de acordo.

Nota: estamos usando um LED azul. Usar uma cor diferente (como o vermelho) exigirá relógios um pouco diferentes; uma configuração de brilho médio para azul já pode ser brilho máximo para vermelho. Isso acontece porque diferentes comprimentos de onda de luz exigirão diferentes quantidades de energia, com as cores mais frias, como roxo e azul, exigindo mais energia, enquanto as cores mais quentes, como vermelho e laranja, requerem menos energia.

entidade led_clkDiv é a porta (present_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; led_clk: out STD_LOGIC); end led_clkDiv; arquitetura O comportamento de led_clkDiv é o sinal tmp_clk: std_logic: = '0'; variável compartilhada max_count: integer; begin count_stuff: process (present_state) begin case present_state é quando "0000" => max_count: = 0; quando "0001" => max_count: = 2; quando "0010" => max_count: = 4; quando "0011" => max_count: = 6; quando "0100" => max_count: = 8; quando "0101" => max_count: = 10; quando "0110" => max_count: = 12; quando "0111" => max_count: = 14; quando "1000" => max_count: = 16; quando "1001" => max_count: = 25; quando "1010" => max_count: = 50; quando "1011" => max_count: = 100; quando "1100" => max_count: = 150; quando "1101" => max_count: = 200; quando "1110" => max_count: = 250; quando "1111" => max_count: = 300; caso final; fim do processo count_stuff; meu_div: processo (clk, tmp_clk, present_state) variável div_cnt: inteiro: = 0; comece if (rise_edge (clk)) then if (div_cnt> = max_count) then tmp_clk <= not tmp_clk; div_cnt: = 0; senão div_cnt: = div_cnt + 1; fim se; fim se; led_clk <= tmp_clk; finalizar processo meu_div; fim Comportamental;

Etapa 3: Criação do controlador de LED

Agora que chegamos até aqui, é hora de finalmente combinar todos os componentes que criamos até agora no arquivo do controlador de LED.

Para resumir, os componentes usados são os seguintes:

- Contador de entrada (updown_counter)

- Divisor de relógio (counter_clkDiv)

- Divisor de relógio LED (led_clkDiv)

- Driver de exibição de sete segmentos (sseg_dec) (arquivo anexado)

O driver de exibição de sete segmentos não foi discutido anteriormente porque, na verdade, pegamos emprestado o arquivo VHDL do Dr. Bryan Mealy devido ao seu código longo e complicado. O que ele essencialmente faz é direcionar nossas entradas de botão para a tela de sete segmentos na placa Basys 3 para que possamos saber o nível de brilho ativado.

Seguindo em frente, o controlador de LED usa flip-flops para aumentar ou diminuir a contagem que controla o display de sete segmentos e o nível de brilho da lâmpada LED simultaneamente.

contador de entidade é a porta (clk: em STD_LOGIC; up_enable: em STD_LOGIC; down_enable: em STD_LOGIC; SEGMENTOS: out STD_LOGIC_VECTOR (7 downto 0); DISP_EN: out STD_LOGIC_VECTOR (3 downto 0); led_clk: out STD_LOGIC); contador final; arquitetura O comportamento do contador é o componente updown_counter é a porta (present_state: out STD_LOGIC_VECTOR (3 downto 0); previous_state: in STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; habilitar para cima: em STD_LOGIC); end component updown_counter; o componente counter_clkDiv é a porta (clk: in std_logic; sclk: out std_logic); end component counter_clkDiv; componente sseg_dec é a porta (ALU_VAL: em std_logic_vector (7 downto 0); SINAL: in std_logic; VALID: in std_logic; CLK: in std_logic; DISP_EN: out std_logic_vector (3 downto 0); SEGMENTOS: out std_logic_vector (7 downto 0); componente final sseg_dec; componente led_clkDiv é a porta (present_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; led_clk: out STD_LOGIC); end component led_clkDiv; sinal estado_atual: STD_LOGIC_VECTOR (3 até 0): = "0000"; sinal próximo_estado: STD_LOGIC_VECTOR (3 até 0): = "0000"; sinalizar estado_ anterior: STD_LOGIC_VECTOR (3 até 0): = "0000"; sinal Alu_Val: STD_LOGIC_VECTOR (7 até 0); sinal sclk: STD_LOGIC; começar Alu_Val (7 até 4) <= "0000"; Alu_Val (3 até 0) <= presente_estado; next_state (0) <= not (present_state (0)); next_state (1) <= present_state (0) xou present_state (1); next_state (2) <= (present_state (0) e present_state (1)) xou present_state (2); next_state (3) <= (present_state (0) e present_state (1) e present_state (2)) xou present_state (3); estado_ anterior (0) <= não (estado_atual (0)); estado_ anterior (1) <= estado_atual (0) xnor estado_atual (1); anterior_estado (2) <= (presente_estado (0) nem presente_estado (1)) xou presente_estado (2); anterior_state (3) sclk, next_state => next_state, previous_state => previous_state, up_enable => up_enable, down_enable => down_enable, present_state => present_state); exibir: mapa da porta sseg_dec (ALU_VAL => Alu_Val, SIGN => '0', VALID => '1', CLK => clk, DISP_EN => DISP_EN, SEGMENTOS => SEGMENTOS); led_div: mapa da porta led_clkDiv (clk => clk, present_state => present_state, led_clk => led_clk); clk_div: mapa da porta counter_clkDiv (clk => clk, sclk => sclk); fim Comportamental;

Etapa 4: Estabelecendo Restrições e Montagem

Restrições

Para configurar e programar adequadamente a placa Basys 3, devemos primeiro configurar nosso arquivo de restrições que está anexado a esta etapa. As seguintes configurações foram ajustadas:

Botões

- Alterado T18 para "up_enable" (aumentar o brilho)

- Alterado U17 para "down_enable" (diminuir o brilho)

Display de 7 segmentos

- W7, W6, U8, V8, U5, V5, U7, V7 representam cada segmento de um display

- U2, U4, V4, W4 representam cada ânodo exibido (apenas 2 estão ativos porque nosso número mais alto é 15)

PMOD Header JC

JC7 é onde conectamos um dos fios da lâmpada LED, e o outro fio leva ao TERRA

Depois de configurar tudo isso, tudo o que você precisa fazer é gerar seu bitstream (com qualquer software que estiver usando, por exemplo, Vivado), programar sua placa e bum! Você conseguiu uma placa de trabalho.

Nota: O mapeamento dos pinos pode ser encontrado na Folha de Dados Basys 3 aqui.

conjunto

Etapa 5: usando seu interruptor Dimmer

Se tudo correr bem, você deve ter um sistema dimmer totalmente funcional. Para resumir, pressionar o botão superior aumentará o brilho (até 15) e pressionar o botão para baixo diminuirá o brilho (até 0). Espero que tudo corra bem para a sua visão agora relaxada!

Recomendado:

Montagem regulável do sensor ultrassônico: 9 etapas (com fotos)

Montagem regulável do sensor ultrassônico: Hi! Eu sou Alejandro. Estou no 8º ano e sou aluno do instituto tecnológico IITA. Para esta competição fiz uma montagem regulável para um sensor ultrassônico para robótica que pode ser acoplado diretamente ao robô ou a um servo, e eu

Painel de LED regulável: 15 etapas (com imagens)

Painel de LED regulável: Quando vi o concurso de LED, fiquei pensando se havia algo que seria divertido de fazer aquele LED usado. Não sou realmente um eletricista, então achei que seria um desafio divertido. Eu estava procurando uma lâmpada de trabalho há algum tempo, então

Holofote LED regulável DIY: 5 etapas (com fotos)

Holofote LED ajustável DIY: holofotes às vezes tendem a parar de funcionar com o passar do tempo, embora hoje em dia eles usem LEDs. Isso pode ser devido a vários motivos, como superaquecimento ou falha no driver do LED ou no processo de fabricação. A maioria de nós acaba jogando fora um bastão

Faça sua própria iluminação de oficina com LED regulável !: 11 etapas (com fotos)

Faça sua própria iluminação de oficina com LED regulável !: Neste manual, mostrarei como fazer sua própria iluminação de LED extremamente eficiente para sua oficina! Nós, fabricantes, nunca temos iluminação suficiente em nossa mesa de trabalho, então precisamos comprar lâmpadas. Mas, como fabricantes, não compramos coisas (e somos roubados …)

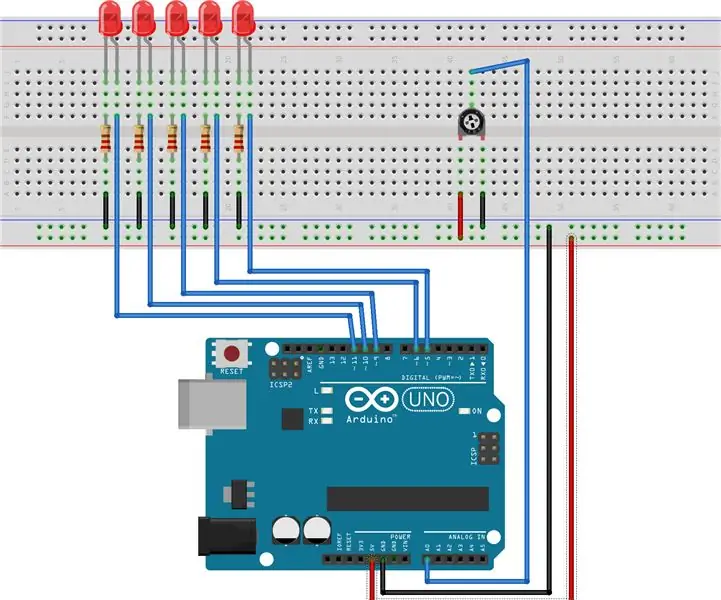

Matriz de LED regulável: 4 etapas

Matriz de LED dimerizável: Este projeto atinge três objetivos principais: - Ler um valor analógico de um potenciômetro - Escrever um valor analógico para cada LED - Variar o brilho de cada LED com base na entrada do potenciômetro Materiais necessários: - 5 leds - Potenciômetro- (5) Resis 220 ohm